|

Глава 6. Контроллер Ethernet (EMAC) - EMAC

Раздел 6.3. Операции и функциональное описание - Operations and Functional Descriptions

6.3. Операции и функциональные описания

6.3.1. Внешние сигналы

Таблица 6-1.

Назначение контактов EMAC RGMII Имя вывода

RGMII_RXD3 / RMII_NULL - RXD3

RGMII_RXD2 / RMII_NULL - RXD2

RGMII_RXD1 / RMII_RXD1 - RXD1

RGMII_RXD0 / RMII_RXD0 - RXD0

RGMII_RXCK / RMII_NULL - RXCK

RGMII_RXCTL / RMII_CRS_DV - RXCTL

RGMII_NULL / RMII_RXER - /

RGMII_TXD3 / RMII_NULL - TXD3

RGMII_TXD2 / RMII_NULL - TXD2

RGMII_TXD1 / RMII_TXD1 - TXD1

RGMII_TXD0 / RMII_TXD0 - TXD0

RGMII_TXCK / RMII_TXCK - TXCK

RGMII_TXCTL / RMII_TXEN - TXCTL

RGMII_CLKIN / RMII_NULL - CLKIN

MDC - MDC

MDIO - MDIO

EPHY_25M - EPHY_25M

Назначение контактов EMAC RMII Имя вывода

RGMII_RXD3 / RMII_NULL - /

RGMII_RXD2 / RMII_NULL - /

RGMII_RXD1 / RMII_RXD1 - RXD1

RGMII_RXD0 / RMII_RXD0 - RXD0

RGMII_RXCK / RMII_NULL - /

RGMII_RXCTL / RMII_CRS_DV - CRS_DV

RGMII_NULL / RMII_RXER - RXER

RGMII_TXD3 / RMII_NULL - /

RGMII_TXD2 / RMII_NULL - /

RGMII_TXD1 / RMII_TXD1 - TXD1

RGMII_TXD0 / RMII_TXD0 - TXD0

RGMII_TXCK / RMII_TXCK - TXCK

RGMII_TXCTL / RMII_TXEN - TXEN

RGMII_CLKIN / RMII_NULL - /

MDC - MDC

MDIO MDIO

EPHY_25M - EPHY_25M

Таблица 6-2. Список контактов EMAC RGMII

Название контакта Описание Тип

RGMII_TXD [3:0] - EMAC RGMII Передача данных - O

RGMII_TXCTL - EMAC RGMII Управление передачей - O

RGMII_TXCK - Тактовая частота передачи EMAC RGMII- O

RGMII_RXD [3:0] - EMAC RGMII Получение данных - I

RGMII_RXCTL - EMAC RGMII Управление приемом - I

RGMII_RXCK - EMAC RGMII Тактовый сигнал приема - I

RGMII_CKIN - EMAC RGMII 125M Reference Clock Input - I

MDC - EMAC Синхроимпульсы данных управления - O

MDIO - EMAC Management Data Input Output - I/O

EPHY_25M - Выход 25 МГц для EMAC PHY - O

Таблица 6-3. Список контактов EMAC RMII Название контакта Описание Тип

RMII_TXD [1:0] - EMAC RMII Передача данных - O

RMII_TXEN - EMAC RMII Transmit Enable - O

RMII_TXCK - EMAC RMII Transmit Clock - I

RMII_RXD [1:0] - EMAC RMII Получение данных - I

RMII_CRS_DV - EMAC RMII Полученные данные действительны - I

RMII_RXER - EMAC RMII Ошибка приема - I

MDC- EMAC Синхроимпульсы данных управления - O

MDIO - EMAC Management Data Input Output - I/O

EPHY_25M - Выход 25 МГц для EMAC PHY - O

Таблица 6-4. Список контактов внутреннего Ethernet PHY Название контакта Описание Тип

EPHY_RTX - EPHY Внешнее сопротивление заземления - AI

EPHY_RXN - Отрицательный выход трансивера EPHY / вход - AI/O

EPHY_RXP - EPHY Трансивер Положительный выход / вход - AI/O

EPHY_TXN - Отрицательный выход трансивера EPHY / вход - AI/O

EPHY_TXP - EPHY Трансивер Положительный выход / вход - AI/O

VCC_EPHY - EPHY Источник питания - P

Таблица 6-5. Тактовые характеристики EMAC

Часы Название Описание Тип

RGMII_TXCK - В режиме RGMII выход 2,5 МГц / 25 МГц / 125 МГц. - O/I

RMII_TXCK - В режиме RMII вход 5 МГц / 50 МГц.

RGMII_RXCK - В режиме RGMII вход 2,5 МГц / 25 МГц / 125 МГц.

RMII_RXCK - В режиме RMII входа нет

RGMII_CLKIN - В режиме RGMII вход опорный тактовый сигнал 125 МГц - I

RMII_CLKIN - В режиме RMII часов нет.

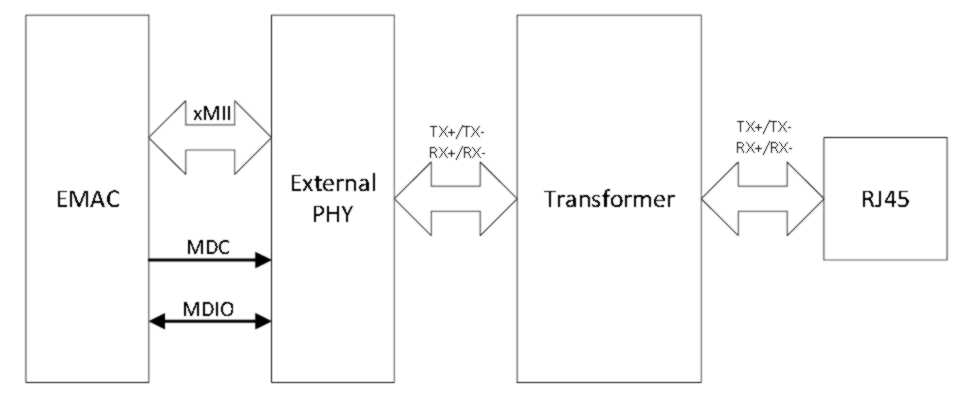

6.3.3. Типичное применение

Рисунок 6-2. Типичное применение EMAC

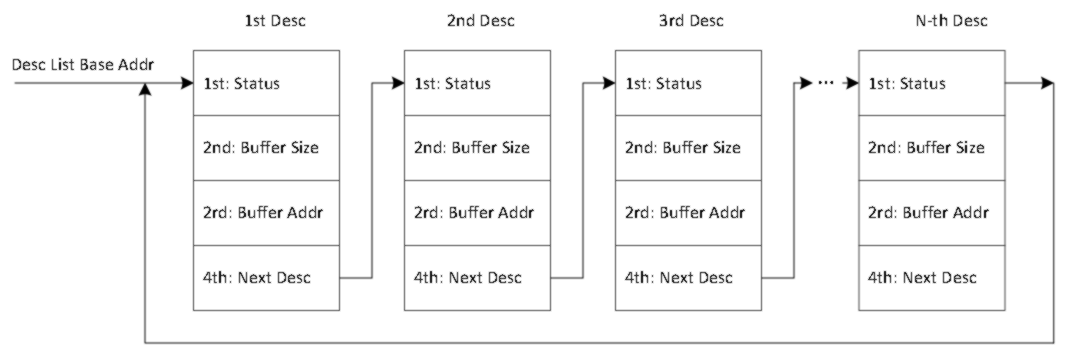

6.3.4. Дескриптор EMAC RX / TX Внутренний DMA EMAC передает данные между памятью хоста и внутренним RX / TX FIFO со связанным списком дескрипторов. Каждый дескриптор состоит из четырех слов и содержит некоторую необходимую информацию для передачи кадров TX и RX. Структура списка дескрипторов показана на рисунке 6-3. Адрес каждого дескриптора должен быть выровнен по 32 бита.

Рисунок 6-3. EMAC RX/TX Descriptor List

6.3.5. Дескриптор передачи

6.3.5.11-е слово дескриптора передачи Биты Описание 31 - TX_DESC_CTL Если установлено, текущий дескриптор может использоваться DMA. Этот бит очищается DMA, когда весь кадр передаются или передаются все данные в буфере текущего дескриптора. 30:17 - Зарезервировано 16 - TX_HEADER_ERR Если установлено, контрольная сумма заголовка переданного кадра неверна. 15 - Зарезервировано 14 - TX_LENGHT_ERR Если установлено, длина передаваемого кадра неверна. 13 - Зарезервировано 12 - TX_PAYLOAD_ERR Если установлено, контрольная сумма полезной нагрузки переданного кадра неверна. 11 - Зарезервировано 10 - TX_CRS_ERR Когда установлено, несущая теряется во время передачи. 9 - TX_COL_ERR_0 Когда установлено, фрейм прерывается из-за конфликта после периода конкуренции. 8 - TX_COL_ERR_1 Если установлено, кадр прерывается из-за слишком большого количества коллизий. 7 - Зарезервировано 6:3 - TX_COL_CNT Количество столкновений до передачи. 2 - TX_DEFER_ERR Если установлено, фрейм прерывается из-за слишком большой задержки. 1 - TX_UNDERFLOW_ERR Если установлено, кадр прерывается из-за ошибки недостаточного заполнения TX FIFO. 0 - TX_DEFER В полудуплексном режиме EMAC откладывает передачу кадра.

6.3.5.22-е слово дескриптора передачи Биты Описание 31 - TX_INT_CTL Когда установлено и текущий кадр был передан, будет установлен TX_INT в регистре состояния прерывания. LAST_DESC 30 - Если установлено, текущий дескриптор является последним для текущего кадра. 29 - FIR_DESC Когда установлено, текущий дескриптор является первым для текущего кадра. 28:27 - CHECKSUM_CTL Эти биты управляют вставкой контрольных сумм в кадр передачи. 26 - CRC_CTL Если установлено, поле CRC не передается. 25:11 - Зарезервировано 10:0 - BUF_SIZE Размер буфера, указанный текущим дескриптором.

6.3.5.33-е слово дескриптора передачи Биты Описание 31:0 - BUF_ADDR Адрес буфера, указанный текущим дескриптором.

6.3.5.44-е слово дескриптора передачи Биты Описание 31:0 - NEXT_DESC_ADDR Адрес следующего дескриптора. Он должен быть выровнен по 32 бита.

6.3.6. Получить дескриптор

6.3.6.11-е слово дескриптора приема Биты Описание 31 - RX_DESC_CTL При установке бита текущий дескриптор может использоваться DMA. Этот бит очищается DMA при получении полного кадра или при заполнении буфера текущего дескриптора. 30 - RX_DAF_FAIL При установке бита текущий кадр не проходит фильтр DA. 29:16 - RX_FRM_LEN Если LAST_DESC не установлен и бит ошибки не установлен, это поле представляет собой длину полученных данных для текущего кадра. Когда установлено LAST_DESC, RX_OVERFLOW_ERR и RX_NO_ENOUGH_BUF_ERR не установлены, это поле является длина приемной рамы. 15 - Зарезервировано 14 - RX_NO_ENOUGH_BUF_ERR При установке бита текущий кадр обрезается из-за нехватки буфера. 13 - RX_SAF_FAIL При установке бита текущая репутация не проходит фильтр SA. 12 - Зарезервировано 11 - RX_OVERFLOW_ERR Когда установлено, произошла ошибка переполнения буфера и текущий кадр неверен. 10 - Зарезервировано 9 - FIR_DESC При установке бита текущий дескриптор является первым дескриптором текущего кадра. 8 - LAST_DESC При установке бита текущий дескриптор является последним дескриптором для текущего кадра. 7 - RX_HEADER_ERR При установке бита контрольная сумма заголовка кадра неверна. 6 - RX_COL_ERR При установке бита возникает поздняя коллизия во время приема в полудуплексном режиме. 5 - Зарезервировано 4 - RX_LENGTH_ERR При установке бита длина текущего кадра неверна. 3 - RX_PHY_ERR При установке бита во время приема утверждается сигнал ошибки приема от PHY. 2 - Зарезервировано 1 - RX_CRC_ERR При установке бита поле CRC полученного кадра неверно. 0 - RX_PAYLOAD_ERR При установке бита контрольная сумма или длина полезной нагрузки полученного кадра неверны.

6.3.6.22-е слово дескриптора приема Биты Описание 31 - RX_INT_CTL При установке бита и получении кадра RX_INT не устанавливается. 30:11 - Зарезервировано 10:0 - BUF_SIZE Размер буфера, указанный текущим дескриптором.

6.3.6.33-слово дескриптора приема Биты Описание 31:0 - BUF_ADDR Адрес буфера, указанный текущим дескриптором.

6.3.6.44-е слово дескриптора приема Биты Описание 31:0 - NEXT_DESC_ADDR Адрес следующего дескриптора. Это поле должно быть выровнено по 32 бита.

|

|