8.1. Аудио-концентратор

8.2. Контроллер микрофона

8.3. Контроллер последовательной аудио-шины

8.4. Аудиокодек

Глава 8. Аудио - Audio

Раздел 8.4. Аудиокодек - Audio Codec

8.4. Аудиокодек

8.4.1. Обзор

Аудиокодек имеет 2-канальный ЦАП с высоким уровнем интеграции смешанных сигналов. DRC со встроенным аппаратным механизмом DAP может использоваться в пути воспроизведения. Аудиокодек имеет следующие особенности:- Поддерживает частоту дискретизации ЦАП от 8 кГц до 192 кГц

- SNR 95 дБ ± 2 дБ при A-weight, THD + N -80 ± 3 дБ, выходной уровень более 0,55 В (среднеквадр.)

- Потребляемая мощность ЦАП 3,0 мА @ 1,8 В

- Поддерживает 16-битное и 20-битное разрешение аудиосэмплов

- Один дифференциальный выход LINEOUTP / N или односторонний выход LINEOUTL / R

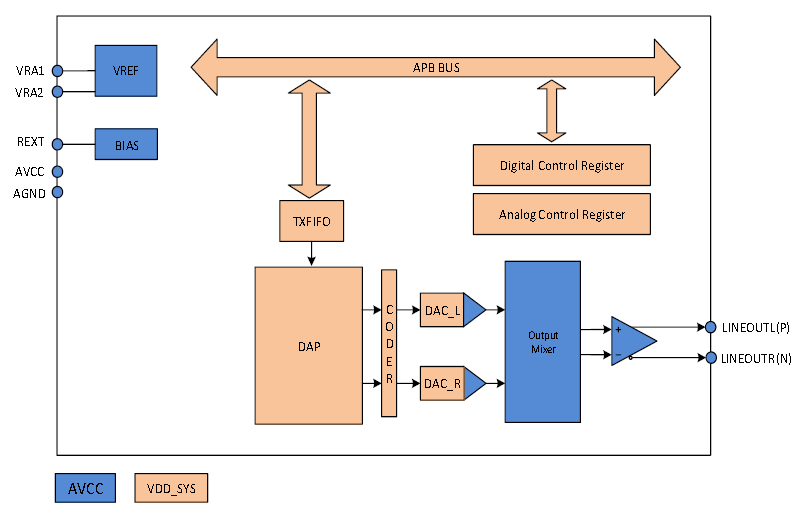

8.4.2. Блок-схема

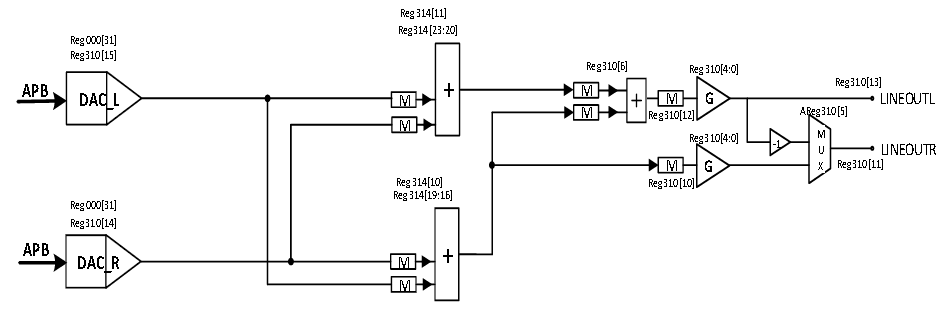

На рисунке 8-19 показана блок-схема аудиокодека.

Рисунок 8-19. Блок-схема аудиокодека

8.4.3. Операции и функциональное описание

8.4.3.1

Внешние сигналы

1. Аналоговые выводы ввода / вывода

Тип сигнала Описание

2. Опорное

Сигнал Тип Описание

REXT AO Внешний опорный вывод VRA1 AO Внутреннее опорное напряжение VRA2 AO Внутреннее опорное напряжение3. Питание / Земля

Сигнал Тип Описание

AVCC P Аналоговая мощность AGND G Аналоговая земля8.4.3.2

Источники синхронизации

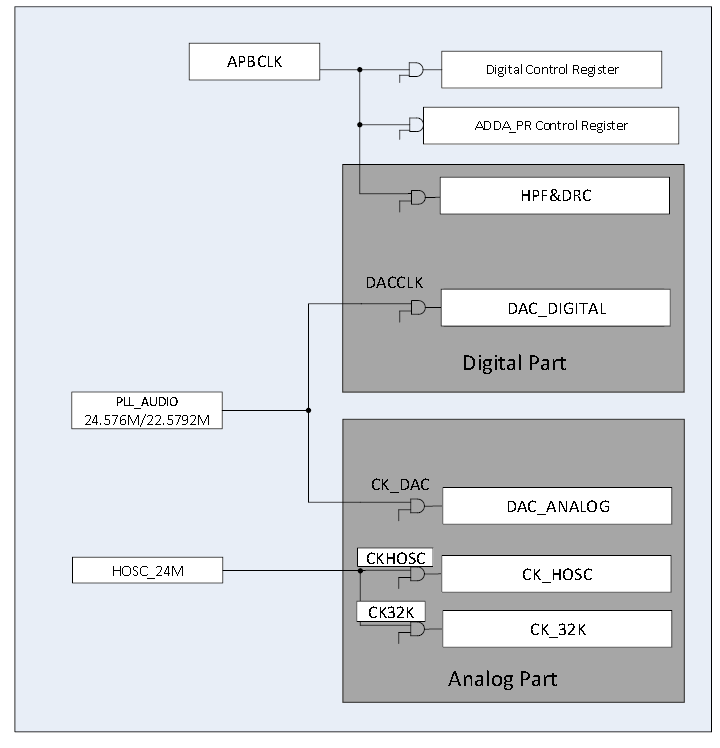

На рисунке 8-20 показан источник тактовой частоты аудиокодека.Пользователи могут видеть CCU для установки часов, конфигурации и информации о стробировании.

Рисунок 8-20. Диаграмма тактовой частоты аудиокодека.

Часы цифровой части от PLL_AUDIO (1X). Часы аналоговой части включают CK_ADC, CK_DAC, CK_DITHER, CK_HOSC, CK_32K. Где CK_ADC, CK_DAC и CK_DITHER предоставляются PLL_AUDIO. CK_HOSC, CK_32K обеспечивается системным генератором 24M. Эти часы должны гарантировать, что VDD-SYS не отключен.

8.4.3.3

Cистема сброса

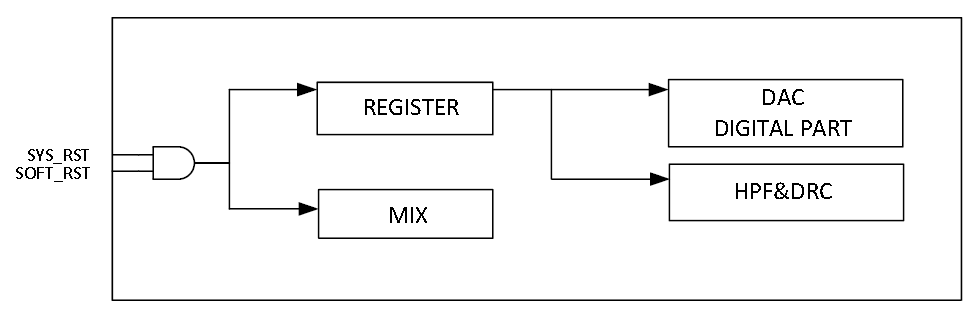

1. Система сброса цифровой части

SYS_RST будет предоставлен доменом VDD_SYS, который происходит из домена VDD_SYS и создается доменом RTC. Каждый домен имеет функцию устранения дребезга, чтобы подтвердить, насколько сильна система сброса. Часть регистра кодека, MIX, будет сброшена SYS_RST во время включения питания или программной записи логики управления сбросом. Остальные части будут сброшены программной конфигурацией через регистр записи.

Рисунок 8-21. Система сброса цифровой части аудиокодека

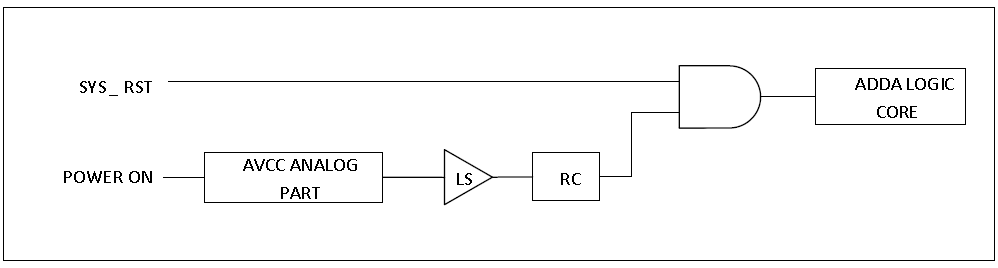

2. Система сброса аналоговой части

Когда AVCC включен, он отправит сигнал AVCC_POR. И сигнал AVCC_POR передает часть сдвига уровня и RC-фильтра в логическое ядро ??ADDA, которое сбрасывает аналоговую часть AVCC.

Рисунок 8-22. Система сброса аналоговой части аудиокодека

8.4.3.4

Схема пути к данным

На рисунке 8-23 показан путь данных аудиокодека.

Рисунок 8-23. Схема тракта передачи данных аудиокодека

8.4.3.5

Стерео ЦАП

Частоту дискретизации стерео ЦАП можно настроить (активировать/деактивировать), установив бит [15:14] бита [31] регистра AC_DAC_DPC.

В целях экономии энергии ЦАП может иметь регистр DAC_REG. Цифровая часть ЦАП может быть включена / отключена битом [31] регистра AC_DAC_DPC.

8.4.3.6

Путь аналогового аудиовыхода

Аудиокодек имеет один порт аналогового вывода:LINEOUT имеет один дифференциальный выход для передачи сигналов линейного уровня на внешнее звуковое оборудование. Источником вывода LINEOUTL (P) является DACL. Источником выходного сигнала LINEOUTR (N) является дифференциальный выход ЦАП. Регулировка громкости логарифмическая с диапазоном 43,5 дБ с шагом 1,5 дБ от -43,5 дБ до 0 дБ. Выходной буфер LINEOUT включается или выключается битами [13] и [11] DAC_REG.

8.4.3.7

Прерывание

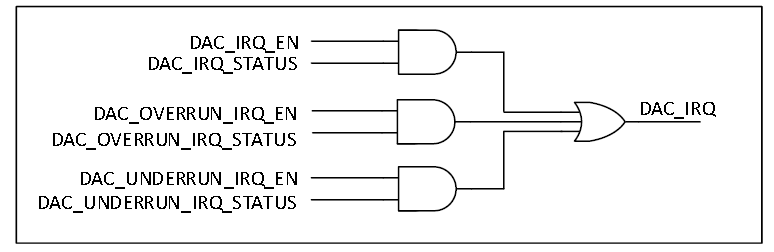

Аудиокодек имеет два прерывания. На рисунке 8-24 описана система прерывания аудиокодека.

Рисунок 8-24. Система прерывания аудиокодека.

8.4.3.8

DAP

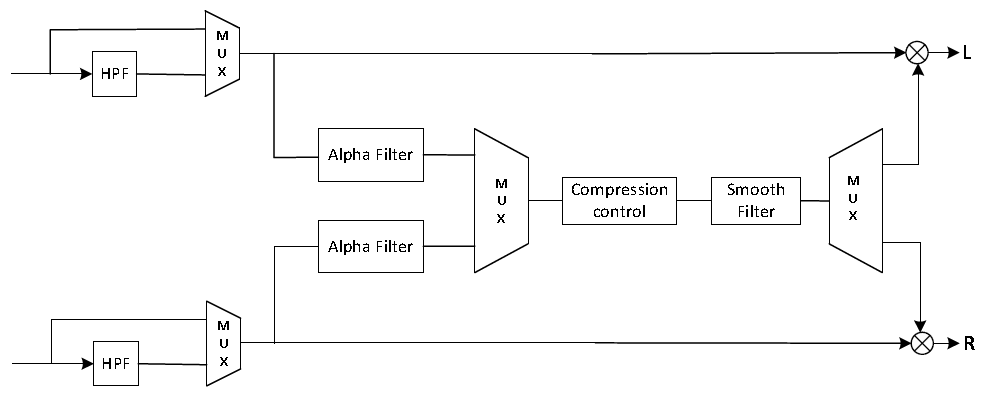

1. Поток данных DAP

Рисунок 8-25. Поток данных DAP

2. Функция DRC

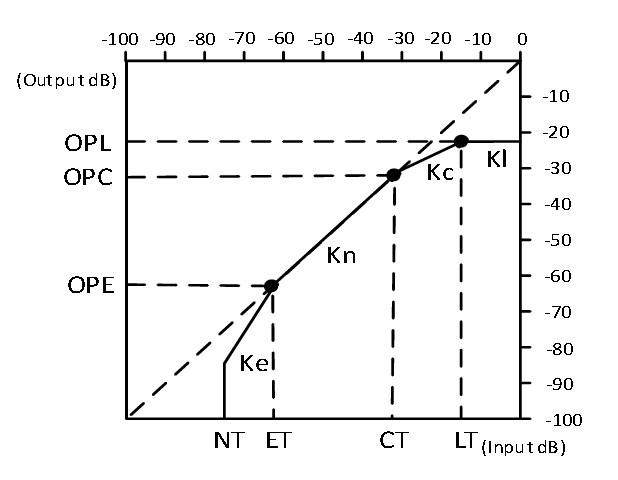

Схема DRC имеет три порога, три смещения и четыре крутизны (все программируемые). Есть один групповой DRC для левого / правого каналов. Схема ввода / вывода DRC следующая.

Рисунок 8-26. Блок-схема DRC

Рисунок 8-27. Параметры статической кривой DRC

Настройка параметров DRC:

Формат числа - N.M, что означает, что слева от десятичной точки находится N битов, включая бит знака, и M битов справа от десятичной точки. Например, «Числа в формате 9,23» означают, что слева от десятичной точки находится 9 битов, а справа - 23 бита.

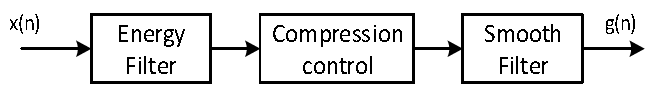

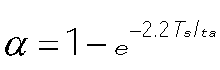

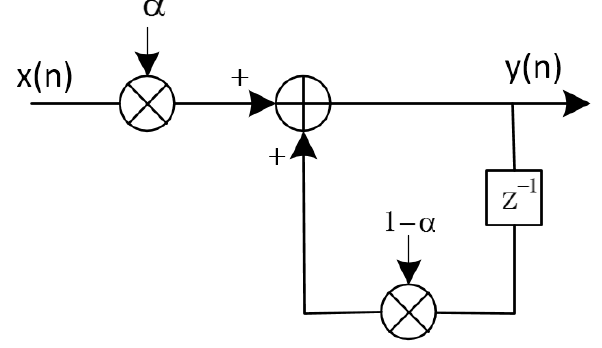

Энергетический фильтр предназначен для оценки RMS-значения потока аудиоданных в DRC и имеет два параметра, которые определяют временное окно, в течение которого RMS должно быть выполнено.

Параметр вычисляется по формуле:

Рисунок 8-29. Структура энергетического фильтра

Контроль сжатия

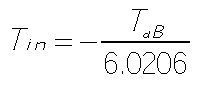

Этот элемент имеет десять параметров (ET, CT, LT, Ke, Kn, Kc, Kl, OPL, OPC, OPE), которые все являются программируемыми, и вычисление будет объяснено следующим образом.

Порог - это значение, определяющее, будет ли сигнал сжиматься или нет. Когда RMS сигнала больше порогового значения, сигнал будет сжат. Значение порогового значения на входе в регистр коэффициентов вычисляется по формуле

Здесь TdB должно быть меньше нуля, положительное значение недопустимо.

Например, желательно установить CT = -40 дБ, тогда для Tin, необходимого для установки CT на -40 дБ, будет CTin = - (-40 дБ) /6.0206 = 6,644, CTin вводится как 32-битное число в формате 8,24.

Следовательно, CTin = 6.644 = 0000 0110.1010 0100 1101 0011 1100 0000 = 0x06A4 D3C0 в формате 8.24.

K - наклон в области сжатия. Например, сжатие n: 1 означает, что увеличение выходного сигнала на 1 дБ составляет для входа n дБ RMS.

Вход K для коэффициента ram вычисляется по формуле K = 1/n

Например, желательно установить 2: 1, тогда для Kc требуется установить 2: 1 - это Kc = 1/2 = 0,5, Kc вводится как 32-битное число в формате 8,24.

Следовательно, Kc = 0,5 = 0000 0000.1000 0000 0000 0000 0000 0000 = 0x0080 0000 в формате 8,24.

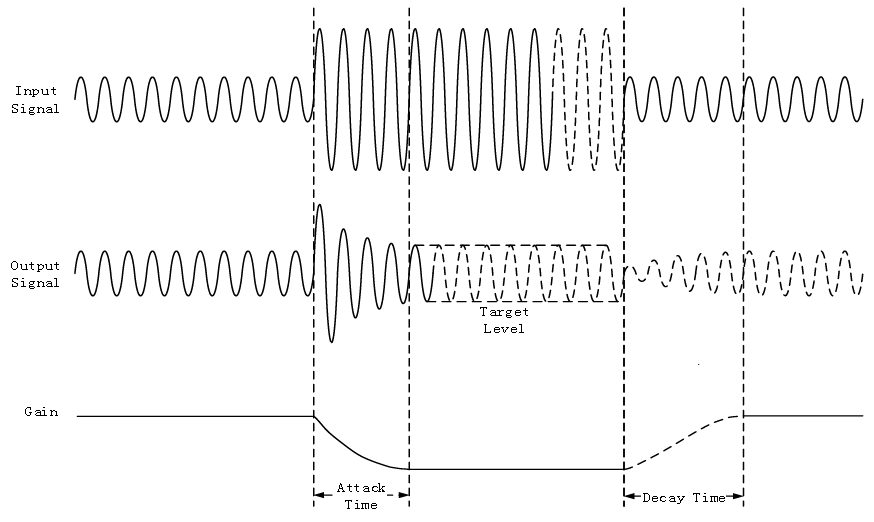

Сглаженный фильтр усиления предназначен для сглаживания усиления и управления соотношением увеличения и уменьшения усиления. Время затухания и атака показаны на Рисунке 8-30.

Структура фильтра Gain Smooth также является альфа-фильтром, поэтому время нарастания вычисление такое же, как и фильтр энергии.

Рисунок 8-30. Плавный фильтр усиления.

8.4.4. Рекомендации по программированию

8.4.4.1

Процесс воспроизведения