Глава 10. Система безопасности - Security System

Раздел 10.1. Криптосистема - Crypto Engine

Система безопасности

10.1.1. Обзор

Модуль Crypto Engine (CE) является одним из ускорителей алгоритмов шифрования / дешифрования. Он поддерживает типы симметричных, асимметричных алгоритмов, алгоритмов хеширования и ГСЧ. Есть два программных интерфейса для безопасного и незащищенного мира. Программный интерфейс прост в настройке, настраивается только управление прерываниями, адрес описания задачи и тег загрузки. Информация управления алгоритмом записывается в память дескриптором задачи, затем CE автоматически считывает ее при выполнении запроса. Он поддерживает параллельные запросы от 4 каналов и имеет внутренний контроллер DMA для передачи данных между CE и памятью. CE имеет следующие особенности:- 128-, 192-, 256-битный размер ключа для AES

- Режимы ECB, CBC, CTR, CTS, OFB, CFB, CBC-MAC для AES

- Поддержка режима AES-CFB CFB1, CFB8, CFB64, CFB128

- AES-CTR поддерживает CTR16, CTR32, CTR64, CTR128

- Режимы ECB, CBC, CTR, CBC-MAC для DES / 3DES

- Режим DES-CTR поддерживает CTR16, CTR32, CTR64

- 256-битный, 512-битный ключ для XTS

- MD5, SHA, HMAC дополняются с использованием оборудования, если не последний пакет, ввод должен быть выровнен с блоком вычислений, а именно 512 бит или 1024 бит

10.1.2. Блок-схема

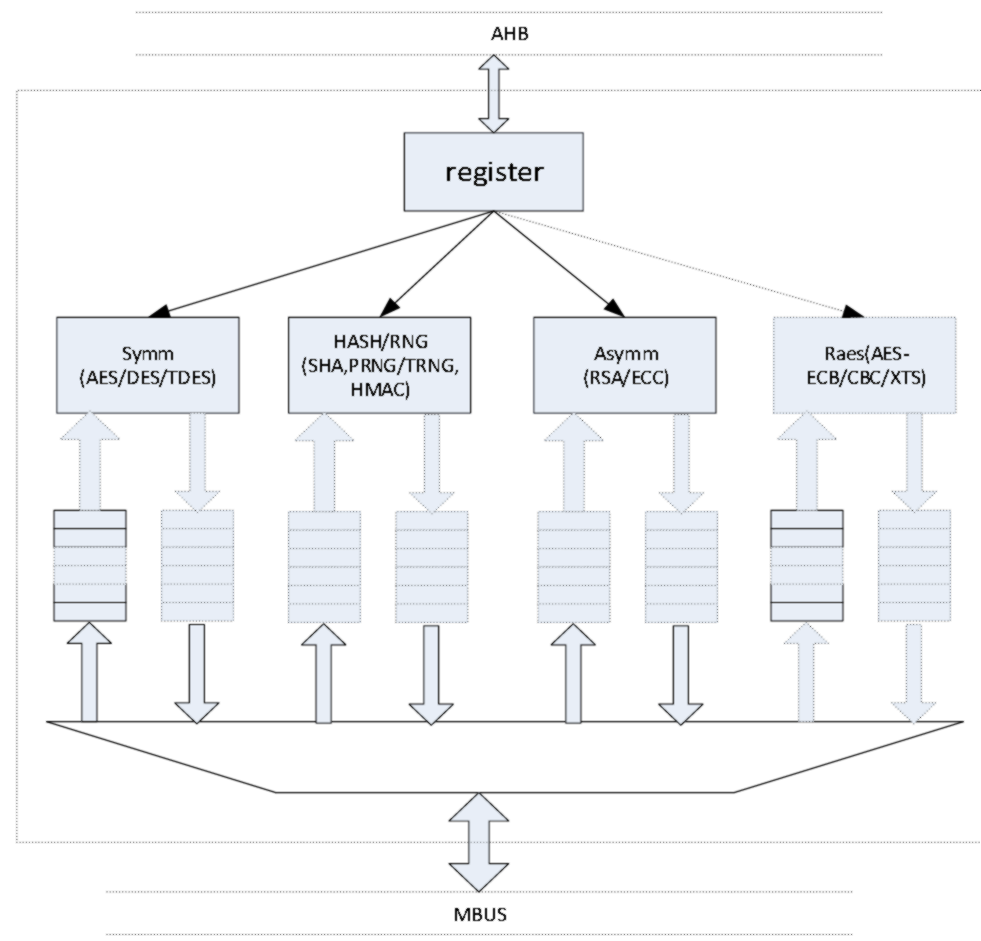

На следующем рисунке показана блок-схема Crypto Engine.

Рисунок 10-1. Блок-схема CE

10.1.3. Операции и функциональные описания

10.1.3.1

Дескриптор задачи

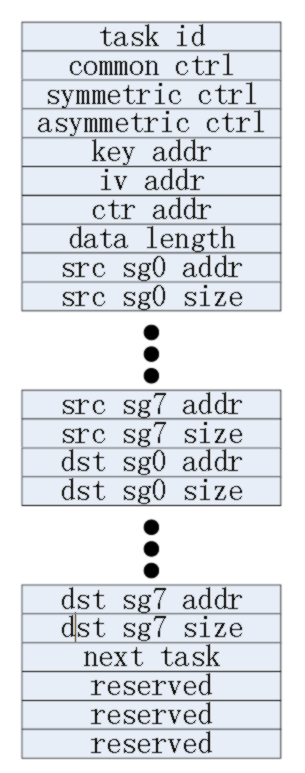

Программное обеспечение делает запрос через дескриптор задачи, предоставляя тип алгоритма, режим, адрес ключа, адрес источника / назначения и размер и т.д. Дескриптор задачи выглядит следующим образом.

Идентификатор цепочки задач поддерживает 0 ~ 3.

10.1.3.2

Общее управление очередью дескриптора задачи

Описание регистра10.1.3.3

Симметричное управление очередью дескриптора задачи

Описание регистра10.1.3.4

Асимметричное управление очередью дескриптора задачи

Описание регистра10.1.3.5

Запрос задачи

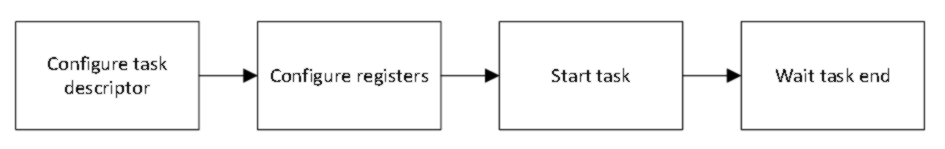

По сути, есть 4 шага для обработки одной задачи из программного обеспечения.

Рисунок 10-3. Процесс запроса задачи

10.1.3.6

Настройка длины данных

10.1.3.7

Охранная операция

Когда ЦП отправляет запрос модулю CE, модуль CE сохраняет безопасный режим ЦП. При выполнении этого запроса этот бит состояния работает как тег доступа для внутреннего и системного ресурса. Для HUK / RSSK / SSK из SID доступ может осуществляться только в безопасном режиме, иначе эти ключи будут использоваться как 0. Для доступа к SID и модулю keyram через шину AHB только безопасный режим может быть успешным, иначе будет считываться 0 или не может написать. При выдаче запросов на чтение и запись MBUS CE будет использовать отправку этого бита безопасного режима на шину, так что безопасный запрос может получить доступ к безопасному и незащищенному пространству, но незащищенный запрос может получить доступ только к незащищенному пространству.10.1.3.8

Параллельная задача

Алгоритмы делятся на 3 типа: симметричные, HASH / RNG, асимметричные. У каждого типа есть очередь задач с 8 элементами для запросов. Задачи в каждой очереди обрабатываются последовательно. Среди этих 3 типов запрос задачи и время завершения не являются точными. Если один тип использует результат другого типа, программное обеспечение должно обеспечивать запуск одного типа после завершения другого типа. CE поддерживает 4 канала в каждом мире и 3 типа алгоритма, которые могут работать параллельно. Когда программное обеспечение выдает запрос, оно сначала проверяет, является ли бит загрузки низким, что означает, что программное обеспечение может запрашивать. Если бит загрузки высокий, что означает, что последний запрос не зарегистрирован CE, программное обеспечение должно дождаться, пока бит загрузки не станет низким. Если программное обеспечение делает несколько запросов одного типа, эти задачи будут выполняться в последовательности запросов. Если программное обеспечение делает несколько запросов разных типов, эти задачи будут выполняться параллельно. Поскольку параллельные задачи будут завершаться не по порядку, программное обеспечение должно делать запрос другого типа с другим идентификатором канала, что приводит к генерации другого бита состояния прерывания.10.1.3.9

Микрокод PKC

Модуль PKC поддерживает асимметричные алгоритмы RSA, ECC в виде микрокода. Он реализует базовые модульные функции сложения, минуса, умножения, добавления точек, двойных точек, логических вычислений и т.д. Полное шифрование RSA / ECC, дешифрование, знак, проверка реализованы с помощью этого микрокода. Асимметричные алгоритмы RSA / ECC реализованы в виде микрокода в модуле PKC. Операции асимметричного шифрования, дешифрования, подписи и проверки выполняются с использованием определенного фиксированного микрокода с оборудованием.10.1.3.10

Конфигурация PKC

10.1.3.11

Проверка ошибок

Модуль CE включает обнаружение ошибок для конфигурации задачи, ошибки вычисления данных и недействительной аутентификации. Когда тип алгоритма в описании задачи считывается в модуль, CE проверит, поддерживается ли этот тип, путем проверки поля типа алгоритма в общем элементе управления. Если значение типа выходит за рамки, CE выдаст сигнал прерывания и установит состояние ошибки. Каждый тип имеет определенный размер входных и выходных данных. После получения дескриптора задачи размер ввода и конфигурация размера вывода будут проверены, чтобы избежать ошибки размера. Если конфигурация размера неверна, CE выдаст сигнал прерывания и установит состояние ошибки. Чтобы защитить ключи от раскрытия, они должны быть помещены в keyram, если запрос с использованием RSSK предназначен для дешифрования AES, а адрес назначения не находится в пространстве keyram, CE не выполнит эту задачу. Он выдаст сигнал прерывания и установит состояние ошибки.10.1.3.12

Синхронизация

Синхросигнал Описание Значения