# 2 System

# 2.1 Memory Mapping

| Module         | Address                      | Size(Bytes)                |  |  |

|----------------|------------------------------|----------------------------|--|--|

| BROM & SRAM    |                              |                            |  |  |

| S_BROM         | 0x0000 00000x0000 AFFF 44 кв |                            |  |  |

| M_BROM         | 0x0001 00000x0001 8FFF       | 36 KB                      |  |  |

|                |                              | 128 KB                     |  |  |

| MCU Local SRAM | 0x0002 00000x0003 FFFF       | The local SRAM is used for |  |  |

|                |                              | system boot.               |  |  |

| SRAM A2        | 0x0004 00000x0006 3FFF       | 16 KB+128 KB               |  |  |

| GPU_SYS        |                              |                            |  |  |

| GPU            | 0x0180 00000x0183 FFFF       | 256 KB                     |  |  |

| VE_SYS         |                              |                            |  |  |

| VE             | 0x01C0 E0000x01C0 EFFF       | 4 KB                       |  |  |

| SP0            |                              |                            |  |  |

| GPIO           | 0x0200 00000x0200 07FF       | 2 KB                       |  |  |

| SPC            | 0x0200 08000x0200 0BFF       | 1 KB                       |  |  |

| PWM0           | 0x0200 0C000x0200 0FFF       | 1 KB                       |  |  |

| CCU            | 0x0200 10000x0200 1FFF       | 4 KB                       |  |  |

| CIR_TX         | 0x0200 30000x0200 33FF       | 1 KB                       |  |  |

| CIR_RX         | 0x0200 50000x0200 53FF       | 1 KB                       |  |  |

| LEDC           | 0x0200 80000x0200 83FF       | 1 KB                       |  |  |

| GPADC_CTRL0    | 0x0200 90000x0200 93FF       | 1 KB                       |  |  |

| THS1           | 0x0200 94000x0200 97FF       | 1 KB                       |  |  |

| LRADC          | 0x0200 98000x0200 9BFF       | 1 KB                       |  |  |

| GPADC_CTRL1    | 0x0200 9C000x0200 9FFF       | 1 KB                       |  |  |

| THS0           | 0x0200 A0000x0200 A3FF       | 1 KB                       |  |  |

| IOMMU          | 0x0201 00000x0201 FFFF       | 64 KB                      |  |  |

| NSI            | 0x0202 00000x0202 FFFF       | 64 KB                      |  |  |

| CPUX_WDT       | 0x0205 00000x0205 0FFF       | 4 KB                       |  |  |

| PWM1           | 0x0205 10000x0205 13FF       | 1 KB                       |  |  |

| NSI_CPU        | 0x0207 10000x0207 13FF       | 1 KB                       |  |  |

| SP1            |                              |                            |  |  |

| UART0          | 0x0250 00000x0250 03FF       | 1 KB                       |  |  |

| UART1          | 0x0250 04000x0250 07FF       | 1 KB                       |  |  |

| UART2          | 0x0250 08000x0250 0BFF       | 1 KB                       |  |  |

| UART3          | 0x0250 0C000x0250 0FFF       | 1 KB                       |  |  |

| Module           | Address Size(Bytes)          |          |

|------------------|------------------------------|----------|

| UART4            | 0x0250 10000x0250 13FF       | 1 KB     |

| UART5            | 0x0250 14000x0250 17FF       | 1 KB     |

| UART6            | 0x0250 18000x0250 1BFF       | 1 KB     |

| UART7            | 0x0250 1C000x0250 1FFF       | 1 KB     |

| TWI0             | 0x0250 20000x0250 23FF       | 1 KB     |

| TWI1             | 0x0250 24000x0250 27FF       | 1 KB     |

| TWI2             | 0x0250 28000x0250 2BFF       | 1 KB     |

| TWI3             | 0x0250 2C000x0250 2FFF       | 1 KB     |

| TWI4             | 0x0250 30000x0250 33FF       | 1 KB     |

| TWI5             | 0x0250 34000x0250 37FF       | 1 KB     |

| SH0              |                              |          |

| SYSCTRL          | 0x0300 00000x0300 0FFF       | 4 KB     |

| CPUX_TIMER       | 0x0300 80000x0300 83FF       | 1 KB     |

| DMAC             | 0x0300 20000x0300 2FFF       | 4 KB     |

| CPUX_MSGBOX      | 0x0300 30000x0300 3FFF       | 4 KB     |

| SPINLOCK         | 0x0300 50000x0300 5FFF       | 4 KB     |

| SID              | 0x0300 60000x0300 6FFF       | 4 KB     |

| CE_NS            | 0x0304 00000x0304 07FF       | 2 KB     |

| CE_S             | 0x0304 08000x0304 0FFF       | 2 KB     |

| SECURE_DEBUG_CFG | 0x0304 20000x0304 23FF       | 1 KB     |

| MEMC             | 0x0310 20000x0330 1FFF       | 2 M      |

| MEMC_SMC         | 0x0311 00000x0311 FFFF       | 64 KB    |

| MEMC_COMMON      | 0x0312 00000x0312 FFFF       | 64 KB    |

| MEMC_DDRC        | 0x0313 00000x0313 FFFF       | 64 KB    |

| MEMC_PHY         | 0x0314 00000x0314 FFFF       | 64 KB    |

| GIC              | 0x0340 00000x034E FFFF       | 15*64 KB |

| SH2              |                              |          |

| NDFC             | 0x0401 10000x0401 1FFF       | 4 KB     |

| SMHC0            | 0x0402 00000x0402 0FFF       | 4 KB     |

| SMHC1            | 0x0402 10000x0402 1FFF       | 4 KB     |

| SMHC2            | 0x0402 20000x0402 2FFF       | 4 KB     |

| SPI0             | 0x0402 50000x0402 5FFF       | 4 KB     |

| SPI1             | 0x0402 60000x0402 6FFF       | 4 KB     |

| SPI2             | 0x0402 70000x0402 7FFF       | 4 KB     |

| USB0             | 0x0410 00000x041F FFFF       | 1 MB     |

| USB1             | 0x0420 00000x042F FFFF       |          |

| GMAC0            | 0x0450 00000x0450 FFFF 64 KB |          |

| GMAC1            | 0x0451 00000x0451 FFFF 64K   |          |

| SPIFC            | 0x047F 00000x047F 0FFF 4 KB  |          |

| PCIE             | 0x0480 00000x04CF FFFF       | 5 MB     |

| Module                     | Address                | Size(Bytes) |  |  |

|----------------------------|------------------------|-------------|--|--|

| USB3                       | 0x04D0 00000x04EF FFFF | 2 MB        |  |  |

| PCIE_USB3_TOP_APP          | 0x04F0 00000x04F7 FFFF | 512 KB      |  |  |

| DE_SYS                     |                        |             |  |  |

| DE                         | 0x0500 00000x053F FFFF | 4 MB        |  |  |

| DI                         | 0x0540 00000x0543 FFFF | 256 KB      |  |  |

| G2D                        | 0x0544 00000x0547 FFFF | 256 KB      |  |  |

| VIDEO0_OUT_SYS             |                        |             |  |  |

| DISPLAY0_TOP               | 0x0550 00000x0550 0FFF | 4 KB        |  |  |

| TCON_LCD0                  | 0x0550 10000x0550 1FFF | 4 KB        |  |  |

| TCON_LCD1                  | 0x0550 20000x0550 2FFF | 4 KB        |  |  |

| TCON_TV0                   | 0x0550 30000x0550 3FFF | 4 KB        |  |  |

| TCON_TV1                   | 0x0550 40000x0550 4FFF | 4 KB        |  |  |

| COMBOPHY_DSI0              | 0x0550 60000x0550 7FFF | 8 KB        |  |  |

| COMBOPHY_DSI1              | 0x0550 80000x0550 9FFF | 8 KB        |  |  |

| HDMI                       | 0x0552 00000x0561 FFFF | 1 MB        |  |  |

| EDP                        | 0x0572 00000x0572 3FFF | 16 KB       |  |  |

| VIDEO1_OUT_SYS             |                        |             |  |  |

| DISPLAY1_TOP               | 0x0573 00000x0573 0FFF | 4 KB        |  |  |

| TCON_LCD2                  | 0x0573 10000x0573 1FFF | 4 KB        |  |  |

| VIDEO_IN_SYS               |                        |             |  |  |

| CSI                        | 0x0580 00000x058F FFFF | 1 MB        |  |  |

| ISP                        | 0x0590 00000x05CF FFFF | 4 MB        |  |  |

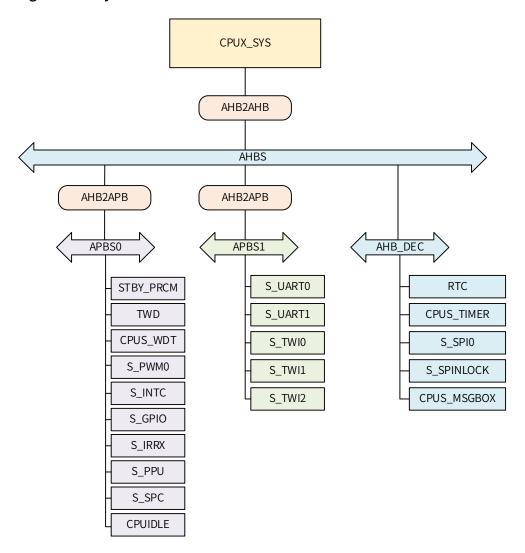

| APBS0                      |                        |             |  |  |

| S_PPU1                     | 0x0700 14000x0700 17FF | 1 KB        |  |  |

| S_SPC                      | 0x0700 20000x0700 23FF | 1 KB        |  |  |

| STBY_PRCM                  | 0x0701 00000x0701 FFFF | 64 KB       |  |  |

| CPUS_WDT                   | 0x0702 04000x0702 07FF | 1 KB        |  |  |

| S_TWD                      | 0x0702 08000x0702 0BFF | 1 KB        |  |  |

| S_PWM0                     | 0x0702 0C000x0702 0FFF | 1 KB        |  |  |

| S_INTC                     | 0x0702 10000x0702 13FF | 1 KB        |  |  |

| S_GPIO                     | 0x0702 20000x0702 27FF | 2 KB        |  |  |

| CPUS_CFG                   | 0x0703 10000x0703 1FFF | 4 KB        |  |  |

| S_CIRRX                    | 0x0704 00000x0704 03FF | 1 KB        |  |  |

| PCK600_CPU                 | 0x0705 00000x0705 FFFF | 64 KB       |  |  |

| PCK600_QCHANNEL(S<br>_PPU) | 0x0706 00000x0706 7FFF | 32 KB       |  |  |

| APBS1                      |                        |             |  |  |

| S_UART0                    | 0x0708 00000x0708 03FF | 1 KB        |  |  |

| S_UART1                    | 0x0708 04000x0708 07FF | 1 KB        |  |  |

| S_TWI0                     | 0x0708 14000x0708 17FF | 1 KB        |  |  |

| S_TWI1                     | 0x0708 18000x0708 1BFF | 1 KB        |  |  |

| Module                             | Address                | Size(Bytes)             |  |  |

|------------------------------------|------------------------|-------------------------|--|--|

| S_TWI2                             | 0x0708 1C000x0708 1FFF | 1 KB                    |  |  |

| AHBS                               |                        |                         |  |  |

| RTC                                | 0x0709 00000x0709 03FF | 1 KB                    |  |  |

| CPUS_TIMER                         | 0x0709 04000x0709 07FF | 1 KB                    |  |  |

| S_SPI0                             | 0x0709 20000x0709 2FFF | 4 KB                    |  |  |

| S_SPINLOCK                         | 0x0709 30000x0709 3FFF | 4 KB                    |  |  |

| CPUS_MSGBOX                        | 0x0709 40000x0709 4FFF | 4 KB                    |  |  |

| MCU_APB0                           |                        |                         |  |  |

| MCU_PRCM                           | 0x0710 20000x0710 2FFF | 4 KB                    |  |  |

| MCU_PWM0                           | 0x0710 30000x0710 33FF | 1 KB                    |  |  |

| AUDIO CODEC                        | 0x0711 00000x0711 0FFF | 4 KB                    |  |  |

| DMIC                               | 0x0711 10000x0711 13FF | 1 KB                    |  |  |

| 12S0                               | 0x0711 20000x0711 2FFF | 4 KB                    |  |  |

| 12S1                               | 0x0711 30000x0711 3FFF | 4 KB                    |  |  |

| 12S2                               | 0x0711 40000x0711 4FFF | 4 KB                    |  |  |

| 12S3                               | 0x0711 50000x0711 5FFF | 4 KB                    |  |  |

| OWA                                | 0x0711 60000x0711 63FF | 1 KB                    |  |  |

| MCU_AHB                            |                        |                         |  |  |

| MCU_DMAC                           | 0x0712 10000x0712 1FFF | 4 KB                    |  |  |

| MCU_TIMER                          | 0x0712 30000x0712 33FF | 1 KB                    |  |  |

| RISCV_SYS                          |                        |                         |  |  |

| RISCV_CFG                          | 0x0713 00000x0713 0FFF | 4 KB                    |  |  |

| RISCV_WDT                          | 0x0713 20000x0713 2FFF | 4 KB                    |  |  |

| RISCV_LCNT                         | 0x0713 40000x0713 4FFF | 4 KB                    |  |  |

| RISCV_MSGBOX                       | 0x0713 60000x0713 6FFF | 4 KB                    |  |  |

| MCU_SRAM                           |                        |                         |  |  |

|                                    |                        | 256 KB (SRAMA3_0 cannot |  |  |

| SRAMA3_0                           | 0x0728 00000x072B FFFF | be used cross 256 KB    |  |  |

|                                    |                        | boundary)               |  |  |

|                                    |                        | 256 KB (SRAMA3_1 cannot |  |  |

| SRAMA3_1                           | 0x072C 00000x072F FFFF | be used cross 256 KB    |  |  |

|                                    |                        | boundary)               |  |  |

| SRAMA3_2                           | 0x0730 00000x0737 FFFF | 512 KB                  |  |  |

| CPUX Related                       |                        |                         |  |  |

| CPU_SUBSYS_CTRL                    | 0x0800 00000x0800 0FFF | 4 KB                    |  |  |

| TIMESTAMP_STA                      | 0x0801 00000x0801 0FFF | 4 KB                    |  |  |

| TIMESTAMP_CTRL                     | 0x0802 00000x0802 0FFF | 4 KB                    |  |  |

| CPU_PLL_CFG                        | 0x0881 70000x0881 7FFF | 4 KB                    |  |  |

| PCIE                               |                        |                         |  |  |

| PCIE_SLV                           | 0x2000 00000x2FFF FFFF | 256 MB                  |  |  |

| RISCV Related (Only RISC-V access) |                        |                         |  |  |

| RISCV_CLINT                        | 0xE000 00000xE000 FFFF | 64 KB                   |  |  |

| Module       | Address                      | Size(Bytes)                                                        |  |

|--------------|------------------------------|--------------------------------------------------------------------|--|

| RISCV_CLIC   | 0xE080 00000xE080 4FFF 20 KB |                                                                    |  |

| RISCV_SYSMAP | 0xEFFF F0000xEFFF FFFF 4 KB  |                                                                    |  |

| DRAM Space   |                              |                                                                    |  |

| DRAM SPACE   | 0x4000 00000x13FFF FFFF      | 4 GB RISC-V core accesses the DRAM address: 0x4004 00000x7FFF FFFF |  |

# 2.2 ARM Cortex<sup>™</sup>-A55 System(CPUX)

#### 2.2.1 Overview

A527 CPU architecture adopts DynamIQ technology. The CPUX system includes DynamIQ Shared Unit (DSU), DynamIQ cluster, GIC600 distributor, CoreSight subsystem, and timestamp module. The features of the CPUX cores and DSU in DynamIQ cluster are as follows.

#### **CPUX Cores**

- Two sets of ARM Cortex<sup>™</sup>-A55 cores in a DynamlQ big. LITTLE configuration

- Memory subsystem features

- 32 KB L1 I-cache and D-cache

- Optional 64KB L2 cache for 'LITTLE' cores

- Optional 128KB L2 cache for 'big' cores

- Separate L1 instruction side memory subsystem with a Memory Management Unit (MMU)

- A64, A32, and T32 instruction sets running on ARMv8-A architecture ISA

- Both the AArch32 and AArch64 execution states at all Exception levels (EL0 to EL3).

- In-order pipeline with direct and indirect branch prediction.

- Optional Data Engine Unit implementing the advanced Single Instruction Multiple Data (SIMD) and floating-point architecture

- Optional Cryptography extensions

- Separate L1 instruction side memory system with a Memory Management Unit (MMU)

- ARM TrustZone® technology

- Generic Interrupt Controller (GIC) interface connecting an external distributor

- Generic Timers interface supporting 64-bit count input from an external system counter

- Reliability, Availability, and Serviceability (RAS) extension

- Debug and trace capabilities

Cryptography extensions are available only when Data Engine unit is present.

#### **DSU**

DSU comprises the L3 cache, the Snoop Control Unit (SCU), internal interfaces to the cores, and external interfaces to the SoC.

- Memory subsystem features

- 1024 KB L3 cache

- Optional 16-way set-associative L3 cache, 64-byte cache line

- L3 memory system can be clocked at a rate synchronous to the external system interconnect or at integer multiples.

- L3 cache partial power down

- Optional cache protection in the form of Error Correcting Code (ECC) on L3 cache RAM instances

- 40-bit, 44-bit, and 48-bit physical addresses

- Main bus interface adopting AMBA 5 ACE protocol or AMBA 5 CHI protocol

- Optional 128-bit wide and I/O-coherent Accelerator Coherency Port (ACP)

- Optional 64-bit wide peripheral port

- ARMv8.2 debug logic

- Supports RAS

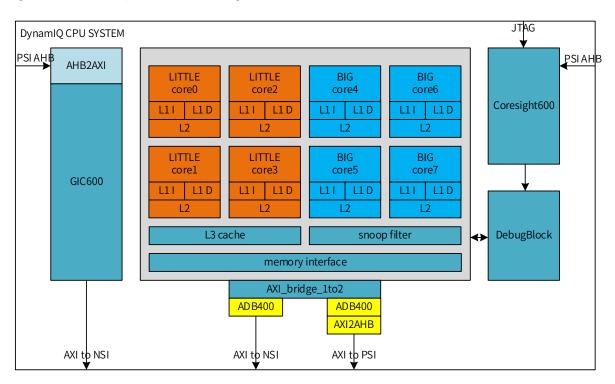

# 2.2.2 Block diagram

The following figure shows the block diagram of CPUX system.

Figure 2-1 CPUX System Block Diagram

The following table describes the components of A527 DynamIQ big. LITTLE cluster.

Table 2-1 CPUX DynamIQ Cluster Components

| Components  | Description                                      |

|-------------|--------------------------------------------------|

| CPU bridges | For communication between cores and DSU buffers. |

| Components           | Description                                                       |  |

|----------------------|-------------------------------------------------------------------|--|

| CCII                 | The SCU maintains coherency and cache-to-cache transmission for   |  |

| SCU                  | all CPUX cores.                                                   |  |

| Dobug and trace      | Each core allows tracing supported by Embedded Trace Macrocell    |  |

| Debug and trace      | (ETM). The trigger events from CPUX cores are transmitted through |  |

| components           | debug APB master/slave interface.                                 |  |

|                      | The cluster supports low power mode and is controlled by a low    |  |

| Clock and power      | power control module outside the cluster power-down domain.       |  |

| management           | DSU and each CPUX core has independent P-channels. They could     |  |

|                      | control the power mode through P-channels.                        |  |

| L3 memory interfaces | To access memory and peripherals.                                 |  |

|                      | Include information related to CPUX core configuration, such as:  |  |

| DCII system control  | Power management of the cluster                                   |  |

| DSU system control   | QOS and ID control of CHI bus                                     |  |

| registers            | DSU hardware configuration information                            |  |

|                      | L3 cache hit and miss count information                           |  |

# 2.2.3 Functional Descriptions

# 2.2.3.1 Power Block System

#### **Power Domain**

The following table describes the power domain of the CPUX.

Table 2-2 CPUX Power domain

| Power<br>Domain | Power Switch | Description                                                                                                          |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------|

| VDD-CPUB        | Yes          | Power source of Core4-Core7. It is controlled by the PPU for each core.                                              |

| VDD-CPUL        | Yes          | Power source of the cluster top and Core0-Core3. It is controlled by the PPU for the cluster top and each core.      |

| VDD-SYS         | No           | Power source of CPUX system excluding the cluster top and CPUX cores. It is the same power supply of the SoC system. |

# Power Mode

CPUX cores support four power modes:

- Debug Recovery

- ON

- OFF (emulated)

- OFF

DSU supports the following power modes

- ON: SFONLY\_ON、1/4 ON、1/2 ON、3/4 ON、FULL ON

- Functional Retention: SFONLY FUNC\_RET, ¼FUNC\_RET, ½FUNC\_RET, ¾FUNC\_RET, FULL FUNC\_RET

- OFF and OFF\_EMU

#### 2.2.3.2 CPU PLL Distribution and Clock Sources

The CPUX system contains three linear frequency modulation PLLs: CPU\_L\_PLL, CPU\_DSU\_PLL, and CPU\_B\_PLL. The following table shows the clock sources of CPUX cores and DSU.

Table 2-3 Clock Sources of CPUX Cores and DSU

| CPUX Cores  | Clock Sources     | Description                                                                      |  |

|-------------|-------------------|----------------------------------------------------------------------------------|--|

|             | CLK32K            |                                                                                  |  |

|             | CLK16M_RC         |                                                                                  |  |

| Core0-Core3 | HOSC              |                                                                                  |  |

|             | PERIO_600M        | Generally, CPU_L_PLL is the main clock                                           |  |

|             | CPU_L_PLL         | source of Core0-Core3. For all clock sources                                     |  |

|             | CLK32K            | of Core0-Core3, refer to CPUA_CLK_REG                                            |  |

|             | CLK16M_RC         | register.                                                                        |  |

| Core4-Core7 | HOSC              | Generally, CPU_B_PLL is the main clock      General Core? For all clock covered. |  |

|             | PERIO_600M        | source of Core4-Core7. For all clock sources                                     |  |

|             | CPU_PLL3CPU_B_PLL | of Core4-Core7, refer to CPUB_CLK_REG                                            |  |

|             | CLK32K            | register.  Generally, CPU_DSU_PLL is the main clock                              |  |

|             | CLK16M_RC         | source of DSU. For all clock sources of DSU,                                     |  |

| DSU         | HOSC              | refer to DSU_CLK_REG register.                                                   |  |

|             | PERIO_600M        | refer to <u>boo_eek_keo</u> register.                                            |  |

|             | PLL_PERIO(2X)     |                                                                                  |  |

|             | CPU_DSU_PLL       |                                                                                  |  |

#### 2.2.3.3 CPUX Reset System

The following table shows the input reset signal of the whole CPUX system.

Table 2-4 Reset signal description of CPUX System

| Reset signal | Sourc<br>e | Description                                                                                                                                                       |

|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBGSYS_RST   | сси        | For detailed information, please refer to the description of DBGSYS_RST in section 2.6.6.70 0x078C DBGSYS Bus Gating Reset Register (Default Value: 0x0000_0000). |

| DSU_RSTN     | PPU        | Whether to reset is controlled by PPU according to the power mode.                                                                                                |

| Reset signal | Sourc<br>e | Description                                                        |

|--------------|------------|--------------------------------------------------------------------|

| CORE_RSTN    | PPU        | Whether to reset is controlled by PPU according to the power mode. |

### 2.2.4 Programming Guidelines

The following takes CPU\_L\_PLL as an example, CPU\_DSU\_PLL and CPU\_B\_PLL are the same.

#### **NOTE**

It is not suggested to enable or disable the PLLs during usage. When the clock is not required, it is recommended to configure the PLL\_OUTPUT\_EN bit of PLL control register as 0.

#### 2.2.4.1 Enabling the Linear Frequency Modulation PLLs

- **Step 1** Write 1 to the PLL\_SSC\_CLK\_SEL bit (bit [29]) of CPU\_L\_PLL\_SSC\_REG register.

- **Step 2** Configure the N, M, and P factors of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 3** Write 1 to the PLL\_PLL\_EN bit (bit [31]) and the PLL\_LDO\_EN bit (bit [30]) of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 4** Write 1 to the LOCK\_ENABLE bit (bit [29]) of the <a href="CPU\_L\_PLL\_CTRL\_REG">CPU\_L\_PLL\_CTRL\_REG</a> register.

- **Step 5** Write 1 to the PLL\_UPDATE bit (bit [26]) of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 6** Wait for the value of the PLL\_UPDATE bit to change to 0.

- **Step 7** Wait for the status of the Lock to change to 1.

- Step 8 Delay 10 ms.

- **Step 9** Write 0 to the PLL\_SSC\_CLK\_SEL bit (bit [29]) of CPU\_L\_PLL\_SSC\_REG register.

#### 2.2.4.2 Configuring the Frequency of Linear Frequency Modulation PLLs

- **Step 1** Configure the PLL\_SSC\_STEP bit (bit [3:0]) of the <u>CPU\_L\_PLL\_SSC\_REG</u> register to select required frequency modulation slope.

- **Step 2** Configure the PLL\_SSC bit (bit [28:12]) of the <u>CPU\_L\_PLL\_SSC\_REG</u> register to set the SSC amplitude.

- **Step 3** Write 1 to the PLL\_SSC\_MODE bit (bit [31]) of the <u>CPU\_L\_PLL\_SSC\_REG</u> register to enable linear frequency modulation.

- **Step 4** Write 1 to the PLL\_UPDATE bit (bit [26]) of the <u>CPU\_L\_PLL\_CTRL\_REG</u> register to update PLL configuration parameters.

- **Step 5** Wait for the value of the PLL\_UPDATE bit to change to 0.

- **Step 6** Configure the N factor of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 7** Write 1 to the PLL\_UPDATE bit (bit [26]) of the <u>CPU\_L\_PLL\_CTRL\_REG</u> register to update PLL configuration parameters.

- **Step 8** Wait for the value of the PLL\_UPDATE bit to change to 0.

- **Step 9** Write 0 to the PLL\_SSC\_MODE bit (bit [31]) of the <u>CPU\_L\_PLL\_SSC\_REG</u> register to disable linear frequency modulation.

- **Step 10** Write 1 to the PLL\_UPDATE bit (bit [26]) of the <u>CPU\_L\_PLL\_CTRL\_REG</u> register to update PLL configuration parameters.

- **Step 11** Wait for the value of the PLL\_UPDATE bit to change to 0.

#### 2.2.4.3 Disabling the Linear Frequency Modulation PLLs

Follow the steps below to disable the PLL:

- **Step 1** Write 0 to the LOCK\_ENABLE bit (bit [29]) of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 2** Write 0 to the PLL\_PLL\_EN bit (bit [31]) and the PLL\_LDO\_EN bit (bit [30]) of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 3** Write 1 to the PLL\_SSC\_CLK\_SEL bit (bit [29]) of CPU\_L\_PLL\_SSC\_REG register.

- **Step 4** Write 1 to the PLL\_UPDATE bit (bit [26]) of the CPU\_L\_PLL\_CTRL\_REG register.

- **Step 5** Wait for the value of the PLL\_UPDATE bit to change to 0.

- **Step 6** Write 0 to the PLL\_SSC\_CLK\_SEL bit (bit [29]) of CPU\_L\_PLL\_SSC\_REG register.

#### 2.2.5 Register list

| Module Name     | Base Address | Description                       |

|-----------------|--------------|-----------------------------------|

| CPU_SUBSYS_CTRL | 0x08000000   | CPU Subsystem Control (4KB)       |

| TIMESTAMP_STA   | 0x08010000   | Timestamp Status Registers (4KB)  |

| TIMESTAMP_CTRL  | 0x08020000   | Timestamp Control Registers (4KB) |

| CPU_PLL_CFG     | 0x08817000   | Cluster PLL configure (4KB)       |

#### 2.2.5.1 CPU\_SUBSYS\_CTRL Register List

| Register Name     | Offset | Description                         |

|-------------------|--------|-------------------------------------|

| GENER_CTRL_REG0   | 0x0000 | General Control Register0           |

| GIC_JTAG_RST_CTRL | 0x000C | GIC and JTAG reset control Register |

| DBG_STATE         | 0x001C | Debug State Register                |

| CPU0_CTRL_REG     | 0x0020 | CPU0 Control Register               |

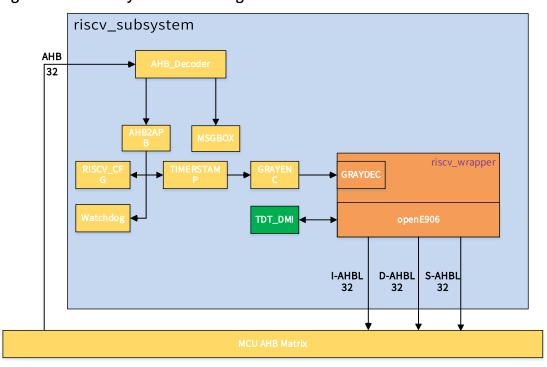

# 2.3 RISC-V System (RISCV)

#### 2.3.1 Overview

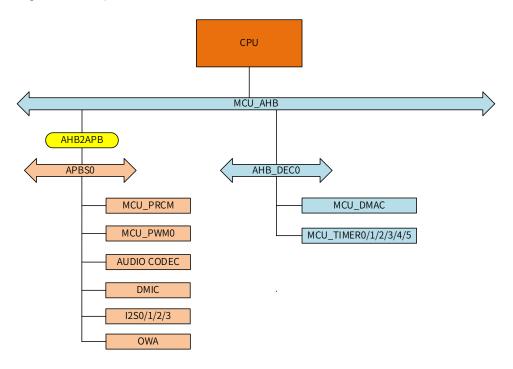

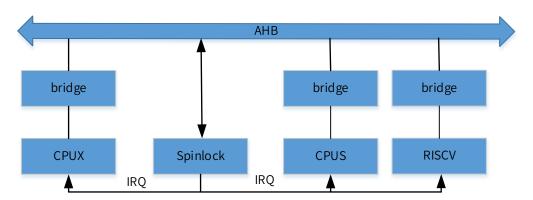

The RISC-V system includes RISC IP core and related peripheral devices (AHB\_Decoder, AHB2APB, RISCV\_CFG, RISC\_TIMESTAMP, and so on), which is able to be interconnected to MCU system by MCU AHB Matrix.

The RISC-V system has the following features:

- Configurable start address via software

- Supports standby in low-power mode and wake-up through external interrupts

- Separate TIMERSTAMP supports timing immediately after reset is released

- Separate watchdog supports to reset the SoC system when the RISC-V system malfunctions

- Separate message box supports communicating with other modules

- Supports separate PMU check module

# 2.3.2 Block Diagram

The following figure shows the block diagram of RISC-V system.

Figure 2-2 RISC-V System Block Diagram

### 2.3.3 Register List

| Module Name | Base Address |

|-------------|--------------|

| RISCV_CFG   | 0x0713_0000  |

# 2.4 GPU

The GPU has the following features:

- ARM G57 MC1 GPU

- Supports OpenGL ES 3.2/2.0/1.1, Vulkan1.1/1.2/1.3, and OpenCL2.2

- Output and input format: 8-bit, 10-bit, and 16-bit YUV

- Anti-aliasing algorithm

- High memory bandwidth and low power consumption in 3D graphics processing

- AMBA4 AXI slave interface

- Latency tolerance

- Texture compression

- Configurable power management

- AFBC1.3

- Supports Digital Rights Management (DRM)

# 2.5 BROM System

#### 2.5.1 Overview

The system has several ways to boot. It has an integrated on-chip Boot ROM (BROM) that is considered the primary program-loader. On the startup process, the A527 starts to fetch the first instruction from address 0x0, where is the BROM located at.

The BROM system is divided into two parts: the firmware exchange launch (FEL) module and the Medium Boot module. FEL is responsible for writing the external data to the local NVM, and Medium Boot is responsible for loading an effective and legitimate BOOT0 from NVM and running.

The BROM system includes the following features:

- Supports CPU0 (the Core0 of ARM CPU) boot process

- Supports mandatory upgrade process through USB and SD card

- Supports GPADC0 pin and eFuse module to select the boot media type

- Supports normal booting and secure booting

- Secure BROM loads only certified firmware

- Ensures that the secure boot is in a trusted environment

### 2.5.2 Functional Description

#### 2.5.2.1 Selecting the Boot Medium

The BROM system supports the following boot media:

- SD Card

- eMMC

- RAW NAND Flash

- SPI NOR Flash (Quad Mode and Single Mode)

- SPI NAND Flash

There are two ways to select the boot medium: GPADC Pin Select and eFuse Select. The BROM will read the state of BOOT\_MODE first, and then select the boot medium according to the state of BOOT\_MODE. The BOOT\_MODE is the BROM\_Config in the eFuse mapping.

The following table shows the BOOT\_MODE setting:

Table 2-5 BOOT\_MODE Setting

| BOOT_MODE[0] | Boot Select type |

|--------------|------------------|

| 0            | GPADC Selection  |

| 1            | eFuse Selection  |

The BOOT\_MODE BIT is bit [0] of the eFuse register 0x03006210.

#### **GPADC Boot Selection**

If the state of the BOOT\_MODE is 0, choose the GPADC Boot Selection.

If BROM failed to boot from the selected medium, it will try other media with the following priority:

And the medium selected by GPADC will be skipped.

For example, when BROM failed to boot from SPI NOR, it will try other media with the following priority:

SPI NOR (selected by GPADC) -> EMMC\_USR -> EMMC\_BOOT -> SLC\_NAND -> MLC\_NAND -> SPI\_NOR (try at first, skipped) -> SPI\_NAND

The following table shows GPADC Boot Select setting.

Table 2-6 GPADC Boot Select Setting

| KEY_VALUE   | Boot Select type                                      |

|-------------|-------------------------------------------------------|

| 0x00-0xB6   | SD Card->MLC NAND->SLC NAND->try (except SPI in PJ)   |

| 0xB7-0x22B  | SD Card->SLC NAND->MLC NAND->try (except SPI in PJ)   |

| 0x22C-0x3AF | SD Card->EMMC_USER->EMMC_BOOT->try (except SPI in PJ) |

| 0x3B0-0x57B | SD Card->EMMC_BOOT->EMMC_USER->try (except SPI in PJ) |

| 0x57C-0x73C | SD Card->SPI NOR->try (except SPI in PJ)              |

| 0x73D-0x8CC | SD Card->SPI NAND->try (except SPI in PJ)             |

| 0x8CD-0xB49 | SD Card->SPI NOR in PJ->try                           |

| 0xB4A-0xE7C | SD Card->SPI NAND in PJ->try                          |

| 0x8CD-0xFFF | Reserved                                              |

When trying SPI NOR, BROM try 4 wire mode first, then 1 wire mode.

#### eFuse Boot Selection

If the state of the BOOT\_MODE is 1, choose the eFuse Boot Selection.

The eFuse\_Boot\_Select\_Cfg is divided into 3 groups and each group is 4-bit. The following table shows the groups of eFuse\_Boot\_Select.

Table 2-7 Groups of eFuse\_Boot\_Select

| eFuse_Boot_Select_Cfg [11:0] | Description         |

|------------------------------|---------------------|

| eFuse_Boot_Select[3:0]       | eFuse_Boot_Select_1 |

| eFuse_Boot_Select_Cfg [11:0] | Description         |  |

|------------------------------|---------------------|--|

| eFuse_Boot_Select[7:4]       | eFuse_Boot_Select_2 |  |

| eFuse_Boot_Select[11:8]      | eFuse_Boot_Select_3 |  |

These three groups take effect with the following priority:

#### eFuse\_Boot\_Select\_1 -> eFuse\_Boot\_Select\_2 -> eFuse\_Boot\_Select\_3

For example, eFuse\_Boot\_Select\_2 will not take effect unless eFuse\_Boot\_Select\_1 is set as 0b1111(skip), eFuse\_Boot\_Select\_3 will not take effect unless eFuse\_Boot\_Select\_2 is set as 0b1111(skip), etc. If all three groups are set to 0b1111, no other groups can be used for boot select, BROM assume "try" is selected.

In the Try mode, the BROM follows the order below to select the boot medium:

#### SD Card -> eMMC -> NAND FLASH -> SPI NOR -> SPI NAND

The following table shows the boot medium priority for the different values of  $eFuse\_Boot\_Select\_n$ , where n = [3:1].

Table 2-8 eFuse Boot Select Setting

| eFuse_Boot_Select_<br>n | Boot media                                                    |  |

|-------------------------|---------------------------------------------------------------|--|

| 0000                    | Try (except SPI in PJ)                                        |  |

| 0001                    | SLC NAND -> MLC NAND                                          |  |

| 0010                    | EMMC_USER -> EMMC_BOOT                                        |  |

| 0011                    | SPINOR                                                        |  |

| 0100                    | SPI NAND                                                      |  |

| 0101                    | MLC NAND -> SLC NAND                                          |  |

| 0110                    | MMC_BOOT -> EMMC_USER                                         |  |

| 1011                    | SPI NOR in PJ                                                 |  |

| 1100                    | SPI NAND in PJ                                                |  |

|                         | When n is 1 or 2:                                             |  |

|                         | The boot medium is decided by the value of eFuse_Boot_Select_ |  |

| 1111 (n + 1).           |                                                               |  |

|                         | When n is 3:                                                  |  |

|                         | Select the boot medium in Try mode.                           |  |

The status of the eFuse boot select pin is the bit [11:0] of the eFuse register 0x03006212.

#### 2.5.2.2 Selecting the Boot Mode

For SoCs that have implemented and enabled the ARM TrustZone technology, there are two boot modes: Normal BROM Mode and Secure BROM Mode.

Secure BROM Mode is designed to protect against attackers modifying the code or data areas in the programmable memory.

During the startup process, the BROM will select the boot mode according to the value of the Secure Enable bit. If the value of Secure Enable bit is 0, the system will boot in Normal BROM Mode. Otherwise, it will boot in Secure BROM Mode.

The System on Chip (SoC) supports the ARM TrustZone technology. If the Secure Enable Bit is enabled, the BROM will be safely booted based on this ARM TrustZone technology.

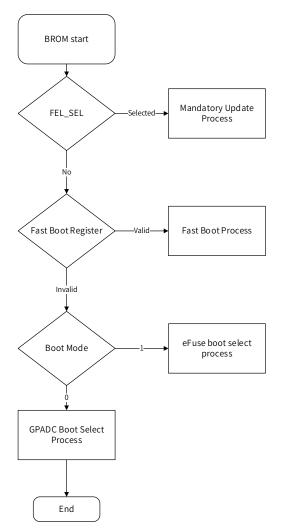

#### Normal BROM Mode

In Normal BROM Mode, the system boot starts from CPU0, and then the BROM will read the state of the FEL pin. If the FEL pin is high, the system will jump to the fast boot process. If it is low, the system will jump to the mandatory upgrade process.

The following figure shows the boot process in Normal BROM Mode.

Figure 2-3 Boot Process in Normal BROM Mode

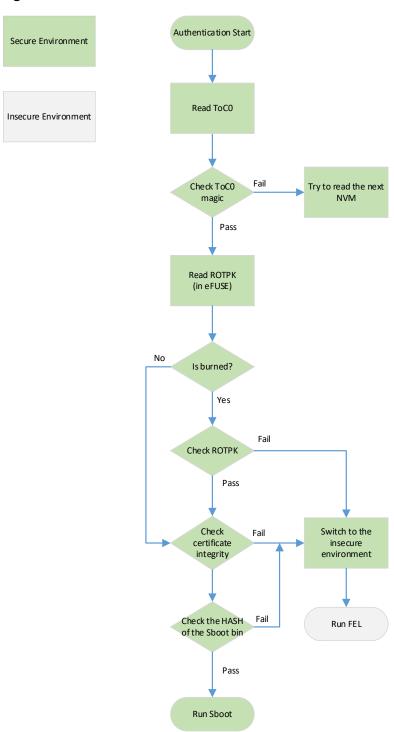

#### Secure BROM Mode

The process of selecting the boot medium in Secure Boot Mode is the same as that in Normal Boot Mode.

In Secure Boot Mode, after the boot medium is selected, the system additionally runs the Security Boot software to authenticate the Sboot bin file.

The following figure shows the authentication process.

Figure 2-4 Authentication Process in Secure BROM Mode

#### **Secure BROM Requirements**

The Secure Boot has the following some requirement:

• Supports X509 certificate

The certificate is used to check whether the Security Boot software is modified or replaced. Before running the Security Boot software, the system checks the integrity of the certificate make sure the software has not been modified or replaced.

- Supports cryptographic algorithms

- AES-128

- SHA-256

- RSA-2048

- AES, DES

The system uses the Crypto Engine (CE) hardware module to accelerate the speed of encryption and decryption. The standard cryptography ensures the reliability of the firmware images. The reliable firmware image ensures that the system security state can be as expected.

• Support OTP/eFuse

#### 2.5.2.3 Mandatory Upgrade Process

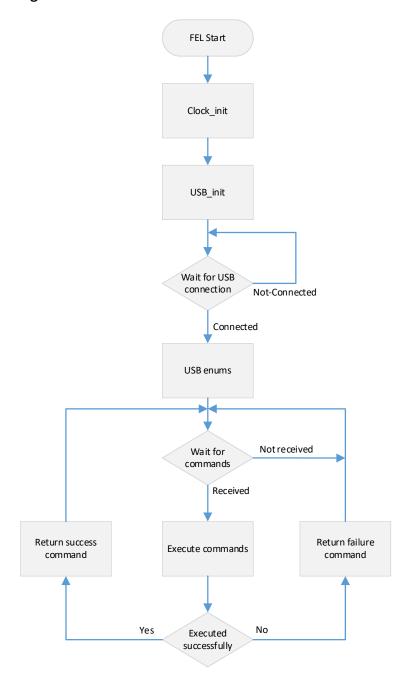

If the FEL pin is detected to pull low, the system will jump to the mandatory upgrade process. The following figure shows the mandatory upgrade process.

Figure 2-5 Mandatory Upgrade Process

The FEL address of the Normal BROM is 0x20.

#### **FEL Process**

When the system enters mandatory upgrade process, it will jump to the FEL process.

The following figure shows the FEL upgrade process.

Figure 2-6 USB FEL Process

#### 2.5.2.4 Fast Boot Process

If the value of the <u>Fast Boot register</u> (0x07090120) in RTC module is not zero, the system will enter the fast boot process. The following table shows the boot medium priority for different values of the Fast Boot register.

Table 2-9 Fast Boot Select Setting

| Reg_bit[31:28] | Boot Select type                                 |

|----------------|--------------------------------------------------|

| 1              | SD Card->MLC NAND -> SLC NAND -> TRY             |

| 2              | SD Card->EMMC_USER -> EMMC_BOOT -> TRY           |

| 3              | SD Card->SPI NOR(1 wire)-> SPI NOR(4 wire)-> TRY |

| 4              | SD Card->SPI NAND -> TRY                         |

| 5              | SD Card->EMMC_BOOT -> EMMC_USER -> TRY           |

| 6              | SD Card->SLC NAND -> MLC NAND -> TRY             |

| 7              | Reserved                                         |

| 8              | SD Card->SPI NOR(4 wire)-> SPI NOR(1 wire)-> TRY |

| 10             | SD Card->SPI NOR(4 wire) in PJ -> TRY            |

| 11             | SD Card->SPI NAND in PJ-> TRY                    |

- The Fast Boot register bit [27:0] is used record the media information.

- Unused value like 7 regarded as "TRY".

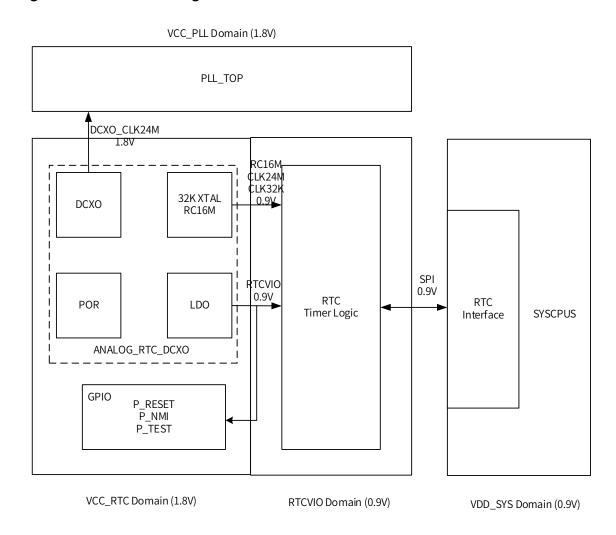

# 2.6 Clock Controller Unit (CCU)

### 2.6.1 Overview

The clock controller unit (CCU) controls the PLL configurations and most of the clock generation, division, distribution, synchronization, and gating. The input signals of the CCU include the external clock for the reference frequency (24 MHz). The outputs from the CCU are mostly clocks to other blocks in the system.

The CCU includes the following features:

- 11 PLLs

- Bus source and divisions

- Clock output control

- Configuring modules clock

- Bus clock gating

- Bus software reset

- There are 16 PLLs in A527. 11 PLLs in CCU, 4 PLLs in CPUX system, and 1 PLL in MCU\_PRCM.

- CCU describes module clocks in CPUX domain excluding the clock of CPUX system.

- For clock description of CPUX system, please refer to section 2.2.3.2 CPU PLL Distribution and Clock Sources.

- For module clocks in CPUS domain, please refer to section 2.12 Power Reset Clock Management (PRCM).

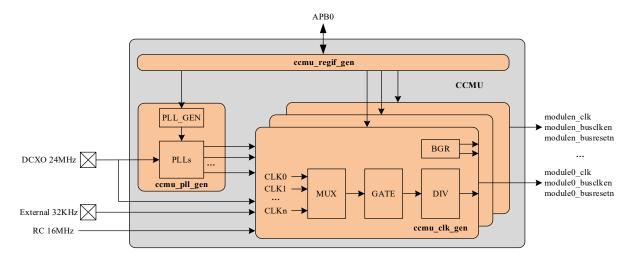

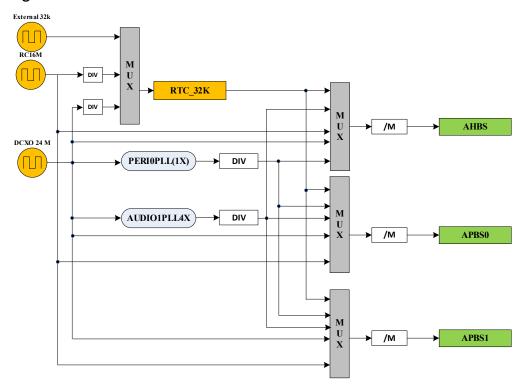

### 2.6.2 Block Diagram

The following figure shows the functional block diagram of the CCU.

Figure 2-7 CCU Block Diagram

# 2.6.3 Functional Description

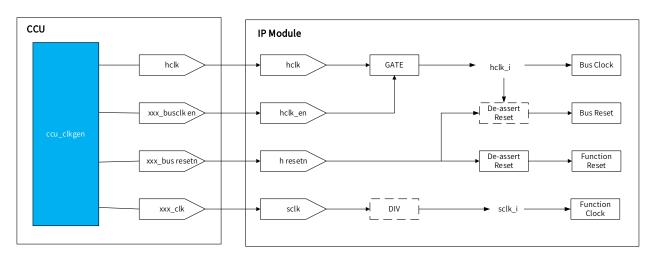

#### 2.6.3.1 Typical Application

Figure 2-8 CCU Typical Application Diagram

CCU outputs bus clock, bus reset, function clock, and function reset to each IP module.

It is needed to enable the bus clock gating signal before using the bus clock. For some subsystems, CCU outputs special bus clock with clock gating added. You also need to enable the bus clock gating signal before using the special bus clock.

The IP reset sources from the synchronous release of the input reset signal. To ensure the synchronous release is implemented in every module, you need to release the reset signal before enabling the clock gating signal of the function clock.

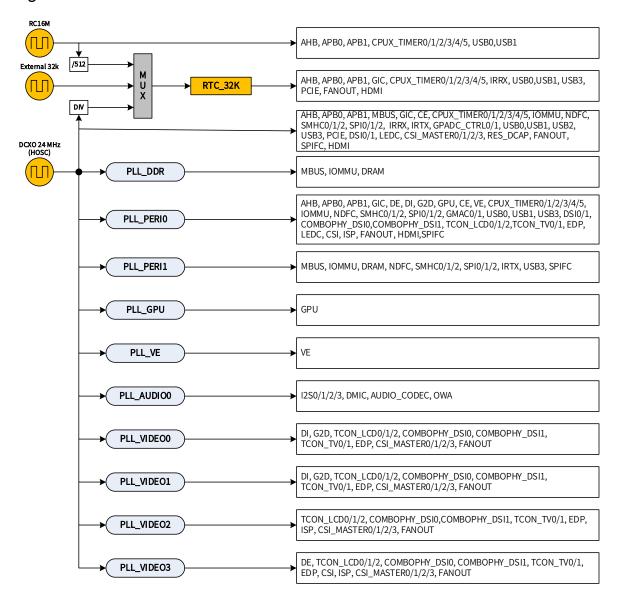

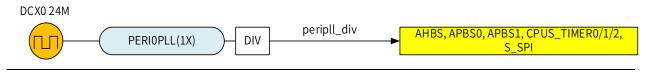

#### 2.6.3.2 PLL Distribution

The following figure shows the block diagram of the PLL distribution.

Figure 2-9 PLL Distribution

#### 2.6.3.3 PLL Features

The following table shows the PLL features.

Table 2-10 PLL Features

| PLL     | Stable Operating Frequency | Actual Operating Frequency | Spread<br>Spectrum | Linear<br>FM | Pk-Pk   | Lock<br>Time |

|---------|----------------------------|----------------------------|--------------------|--------------|---------|--------------|

| PLL_DDR | 1.26 GHz~2.52 GHz          | < 2.5 GHz                  | Yes                | No           | < 200ps | 500us        |

| PLL        | Stable Operating Frequency | Actual Operating Frequency                                                     | Spread<br>Spectrum | Linear<br>FM | Pk-Pk   | Lock<br>Time |

|------------|----------------------------|--------------------------------------------------------------------------------|--------------------|--------------|---------|--------------|

| PLL_GPU    | 1.26 GHz~2.52 GHz          | < 1.5 GHz                                                                      | Yes                | No           | < 200ps | 500us        |

| PLL_PERI0  | 1.26 GHz~2.52 GHz          | 2x: 1.2 GHz<br>3x: 800 MHz<br>5x: 480 MHz                                      | Yes                | No           | < 200ps | 500us        |

| PLL_PERI1  | 1.26 GHz∼2.52 GHz          | 2x: 1.248 GHz/1.2<br>GHz<br>3x: 832 MHz/800<br>MHz<br>5x: 499.2 MHz/480<br>MHz | Yes                | No           | <200ps  | 500us        |

| PLL_VE     | 1.26 GHz~2.52 GHz          | < 1.5 GHz                                                                      | Yes                | No           | < 200ps | 500us        |

| PLL_AUDIO0 | 1.26 GHz~2.52 GHz          | 1x: 22.5792 MHz<br>4x: 22.5792*4 MHz                                           | Yes                | No           | < 200ps | 500us        |

| PLL_VIDEO  | 1.26 GHz~2.52 GHz          | 3x:792 MHz<br>4x:1188 MHz                                                      | Yes                | No           | < 200ps | 500us        |

# 2.6.4 Programming Guidelines

It is not suggested to enable or disable the PLLs frequently during usage. Because the enabling and disabling of PLL will cause a mutual interference between PLLs, which will affect system stability. When the clock is not required, it is recommended to configure the PLL\_OUTPUT\_GATE bit of PLL control register as 0 instead of writing 0 to the enable bit.

# 2.6.4.1 Enabling the PLL

Follow the steps below to enable the PLL:

- **Step 1** Configure the N, M, and P factors of the PLL control register.

- **Step 2** Write 1 to the PLL\_EN bit (bit [31]) and the PLL\_LDO\_EN bit (bit [30]) of the PLL control register, write 0 to the PLL\_OUTPUT\_GATE bit (bit [27]) of the PLL control register.

- **Step 3** Write 1 to the LOCK\_ENABLE bit (bit [29]) of the PLL control register.

- **Step 4** Wait for the status of the Lock to change to 1.

- **Step 5** Delay 20 us.

- **Step 6** Write the PLL\_OUTPUT\_GATE bit (bit [27]) of the PLL control register to 1 and then the PLL will be available.

#### 2.6.4.2 Configuring the Frequency of General PLLs

- **Step 1** Make sure the PLL is enabled. If not, refer to section 2.6.4.1 Enabling the PLL to enable the PLL.

- **Step 2** Configure the PLL\_OUTPUT\_GATE bit (bit [27]) of the PLL control register as 0 to disable the output gate of the PLL. Because, general PLLs are unavailable in the process of frequency modulation.

- **Step 3** Configure the N and M factors. (It is not suggested to configure M1 factor)

- **Step 4** Write 0 and then write 1 to the LOCK\_ENABLE bit (bit [29]) of the PLL control register.

- **Step 5** Wait for the LOCK bit (bit [28]) of the PLL control register to 1.

- **Step 6** Configure PLL\_OUTPUT\_GATE bit (bit [27]) of the PLL control register to 1.

#### 2.6.4.3 Configuring the Frequency of PLL\_AUDIO0

The frequency configuration formula of PLL\_AUDIO0:

#### PLL\_AUDIO0 = 24 MHz\*N/M0/M1/P

PLL\_AUDIO0 does not support dynamic adjustment because changing any parameter of N, M0, M1, and P will affect the normal work of PLL, and the PLL will need to be relocked.

Generally, PLL\_AUDIO0 only needs two frequency points: 24.576\*4 MHz or 22.5792\*4 MHz. For these two frequencies, there are usually special recommended matching factors. To implement the desired frequency point of PLL\_AUDIO0, you need to use the decimal frequency-division function, so follow the steps below:

- **Step 1** Configure the N, M0, M1 and P factors.

- **Step 2** Write 1 to the PLL\_SDM\_EN bit (bit [24]) of PLL\_AUDIOO\_CTRL register.

- **Step 3** Configure PLL\_AUDIO0\_PAT0\_CTRL register to enable the digital spread spectrum.

- **Step 4** Write 0 and then write 1 to the LOCK ENABLE bit (bit [29]) of PLL\_AUDIO0\_CTRL register.

- **Step 5** Write 1 to the LOCK bit (bit [28]) of PLL\_AUDIOO\_CTRL register.

- When the P factor of PLL\_AUDIO0 is an odd number, the clock output is an unequal-duty-cycle signal.

- A527 includes PLL\_AUDIO0 and PLL\_AUDIO1. For detailed description of PLL\_AUDIO1, please refer to section 2.12 Power Reset Clock Management (PRCM).

### 2.6.4.4 Disabling the PLL

Follow the steps below to disable the PLL:

- **Step 1** Write 0 to the PLL\_EN bit (bit [31]) and the PLL\_LDO\_EN bit (bit [30]) of the PLL control register.

- **Step 2** Write 0 to the LOCK\_ENABLE bit (bit [29]) of the PLL control register.

#### 2.6.4.5 Implementing Spread Spectrum

The spread spectrum technology is to convert a narrowband signal into a wideband signal. It helps to reduce the effect of electromagnetic interference (EMI) associated with the fundamental frequency of the signal.

For the general PLL frequency, the calculation formula is as follows:

$$f = \frac{N+1+X}{P\cdot(M0+1)\cdot(M1+1)} \cdot 24MHz, \ 0 < X < 1$$

Where,

P is the frequency division factor of module or PLL;

M0 is the post-frequency division factor of PLL;

M1 is the pre-frequency division factor of PLL;

N is the frequency doubling factor of PLL;

X is the amplitude coefficient of the spread spectrum.

The parameters N, P, M1, and M0 are for the frequency division.

When M1 = 0, M0 = 0, and P = 1 (no frequency division), the calculation formula of PLL frequency can be simplified as follows:

$$f = (N+1+X) \cdot 24MHz, \ 0 < X < 1$$

$[f_1, f_2] = (N+1+[X_1, X_2]) \cdot 24MHz$

$SDM\_BOT = 2^{17} \cdot X_1$

WAVE\_STEP =  $2^{17} \cdot (X_2 - X_1)/(24 \text{ MHz}/PREQ) \cdot 2$

Where, SDM\_BOT and WAVE\_STEP are bits of the PLL pattern control register, and PREQ is the frequency of the spread spectrum.

Different PLLs have different calculate formulas, refer to the CTRL register of the corresponding PLL in section 2.6.6 Register Description.

Follow the steps below to implement the spread spectrum:

#### **Step 1** Configure the control register of the corresponding PLL

- a) Calculate the factor N and decimal value X according to the PLL frequency and PLL frequency formula. Refer to the control register of the corresponding PLL (named PLL\_xxx\_CTRL\_REG, where xxx is the module name) in 2.6.6 Register Description for the corresponding PLL frequency formula.

- b) Write M0, M1, N, and PLL frequency to the PLL control register.

- c) Configure the PLL\_SDM\_EN bit (bit [24]) of the PLL control register to 1 to enable the spread spectrum function.

#### **Step 2** Configure the pattern control register of the corresponding PLL

- a) Calculate the SDM\_BOT and WAVE\_STEP of the pattern control register according to decimal value X and spread spectrum frequency (the bit [18:17] of the PLL pattern register)

- b) Configure the spread spectrum mode (SPR\_FREQ\_MODE) to 2 or 3.

- c) If the PLL\_INPUT\_DIV2 of the PLL control register is 1, configure the spread spectrum clock source select bit (SDM\_CLK\_SEL) of the PLL pattern control register to 1. Otherwise, configure SDM\_CLK\_SEL to the default value 0.

- d) Write SDM\_BOT, WAVE\_STEP, PREQ, SPR\_FREQ\_MODE, and SDM\_CLK\_SEL to the PLL pattern control register, and configure the SIG\_DELT\_PAT\_EN bit (bit [31]) of this register to 1.

Step 3 Delay 20 us

#### 2.6.4.6 Configuring Bus Clock

The bus clock supports dynamic switching, but the process of switching needs to follow the following two rules.

- From a higher frequency to a lower frequency: switch the clock source first, and then set the frequency division factor;

- From a lower frequency to a higher frequency: configure the frequency division factor first, and then switch the clock source.

The bus frequency for each bus is as follows:

- AXI: It is suggested to be configured as the CPU clock frequency divided by 3. when the CPU clock frequency is less than 1.2 GHz, AXI frequency could be configured as the CPU clock frequency divided by 2.

- AHB: Maximum 200 MHz

- APB0: Maximum 100 MHz

- APB1: Maximum 160 MHz

• MBUS: Maximum 700 MHz

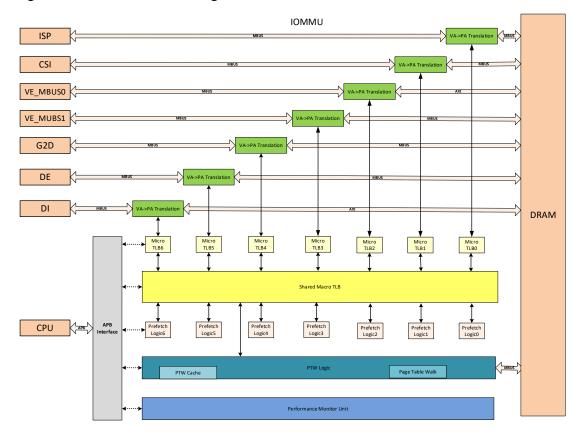

• IOMMU: Maximum 600 MHz

#### 2.6.4.7 Configuring Module Clock

For the Bus Gating Reset register of a module, the reset bit is de-asserted first, and then the clock gating bit is enabled to avoid potential problems caused by the asynchronous release of the reset signal.

For all module clocks except the DDR clock, configure the clock source and frequency division factor first, and then release the clock gating (that is, set to 1). For the configuration order of the clock source and frequency division factor, follow the rules below:

- With the increasing of the clock source frequency, configure the frequency division factor before the clock source:

- With the decreasing of the clock source frequency, configure the clock source before the frequency division factor.

### 2.6.5 Register List

- Before switching the glitch-free MUX, ensure that

- Every clock source is in use.

- The switching time is longer than two clock periods of the slowest clock source.

- Before switching the normal MUX, ensure that the clock sources are closed.

| Module Name | Base Address |

|-------------|--------------|

| CCU         | 0x0200 1000  |

| Register Name       | Offset | Description                 |

|---------------------|--------|-----------------------------|

| PLL_DDR_CTRL_REG    | 0x0010 | PLL_DDR Control Register    |

| PLL_PERIO_CTRL_REG  | 0x0020 | PLL_PERIO Control Register  |

| PLL_PERI1_CTRL_REG  | 0x0028 | PLL_PERI1 Control Register  |

| PLL_GPU_CTRL_REG    | 0x0030 | PLL_GPU Control Register    |

| PLL_VIDEO0_CTRL_REG | 0x0040 | PLL_VIDEO0 Control Register |

| PLL_VIDEO1_CTRL_REG | 0x0048 | PLL_VIDEO1 Control Register |

| PLL_VIDEO2_CTRL_REG | 0x0050 | PLL_VIDEO2 Control Register |

| PLL_VE_CTRL_REG     | 0x0058 | PLL_VE Control Register     |

| PLL_VIDEO3_CTRL_REG | 0x0068 | PLL_VIDEO3 Control Register |

| PLL_AUDIO0_CTRL_REG | 0x0078 | PLL_AUDIO0 Control Register |

# 2.7 DMA Controller (DMAC)

#### 2.7.1 Overview

The Direct Memory Access (DMA) is a method of transferring data between peripherals and memories (including the SRAM and DRAM) without using the CPU. It is an efficient way to offload data transfer duties from the CPU. Without DMA, the CPU has to control all the data transfers. While with DMA, the DMAC directly transfers data between a peripheral and a memory, between peripherals, or between memories.

The DMAC has the following features:

- Up to 16-ch DMA in CPUX domain and 16-ch DMA in CPUS domain

- Provides 53 peripheral DMA requests for data reading and 53 peripheral DMA requests for data writing

- Transferring data with linked list

- Flexible data width: 8 bits, 16 bits, or, 32 bits

- Programmable DMA burst length

- DRQ response includes waiting mode and handshake mode

- Supports non-aligned transform for memory devices

- DMA channels that support the following:

- Pausing DMA

- BMODE and I/O speed mode

- DMA timeout

The following description focuses on the DMA of the CPUX domain.

# 2.7.2 Block Diagram

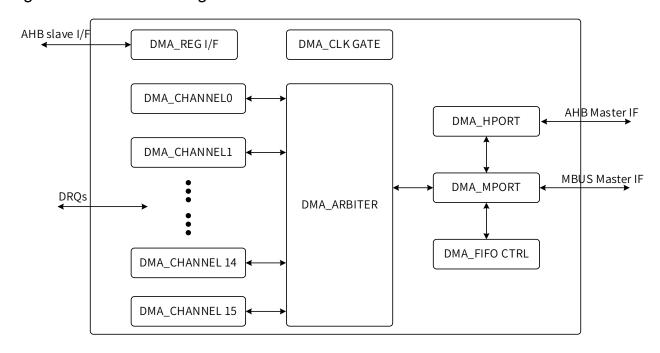

The following figure shows a block diagram of DMAC.

Figure 2-10 DMAC Block Diagram

DMAC contains the following sub-blocks:

Table 2-11 DMAC Sub-blocks

| Sub-block            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA_ARBITER          | Arbitrates the DMA read/write requests from all channels, and converts the requests to the read/write requests of ports.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMA_CHANNELs         | DMA transfer engine. Each channel is independent. When the DMA requests from multiple peripherals are valid simultaneously, the channel with the highest priority starts data transfer first. The system uses the polling mechanism to decide the priorities of DMA channels. When DMA_ARBITER is idle, channel 0 has the highest priority, whereas channel 15 has the lowest priority. When DMA_ARBITER is busy processing the request from channel n, channel (n+1) has the highest priority. For n = 15, the channel (n + 1) should be channel 0. |

| DRQs                 | DMA requests. Peripherals use the DMA request signals to request a data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DMA_MPORT            | Receives the read/write requests from DMA_ARBITER, and converts the requests to the corresponding MBUS access requests. It is mainly used for accessing the DRAM.                                                                                                                                                                                                                                                                                                                                                                                    |

| DMA_HPORT            | The port for accessing the AHB Master. It is mainly used for accessing the SRAM and IO devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DMA_FIFO CTRL        | Internal FIFO cell control module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DMA_REG<br>Interface | DMA_REG is the common register module that is mainly used to resolve AHB commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sub-block   | Description                                        |

|-------------|----------------------------------------------------|

| DMA_CLKGATE | The control module for hardware auto clock gating. |

The DMAC integrates 16 independent DMA channels and each channel has an independent FIFO controller. When the DMA channel starts, the DMAC gets a DMA descriptor from the DMA\_DESC\_ADDR\_REG and uses it as the configuration information for the data transfer of the current DMA package. Then the DMAC can transfer data between the specified devices. After transferring a DMA package, the DMAC judges if the current channel transfer is finished via the linked address in the descriptor. If the linked address shows all the packages are transferred, the DMAC will end the chain transmission and close the channel.

### 2.7.3 Functional Description

#### 2.7.3.1 Clock

The DMAC is on AHB or MBUS. The clocks of AHB and MBUS influence the transfer efficiency of the DMAC.

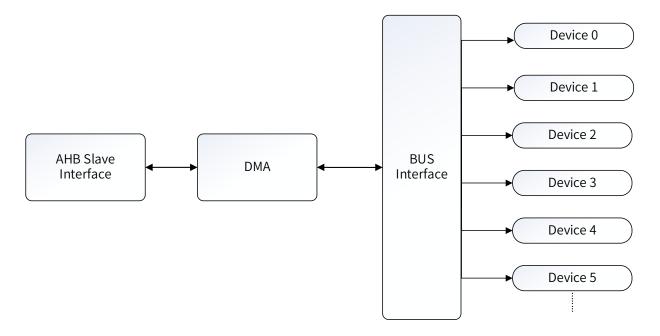

#### 2.7.3.2 Typical Application

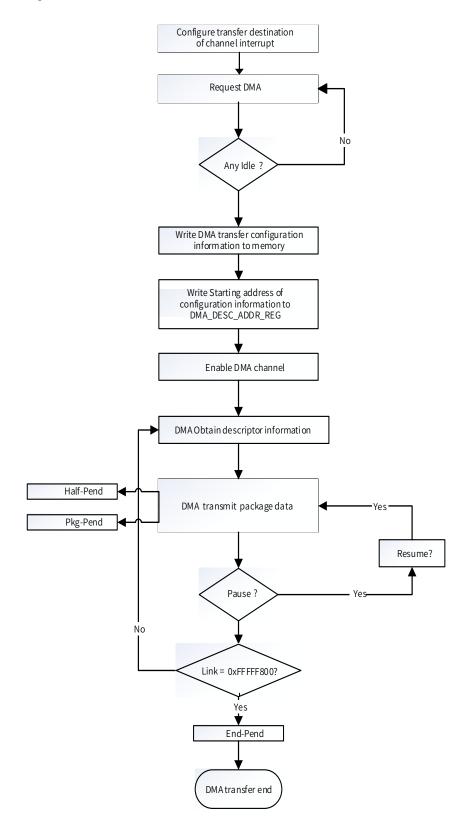

The following figure shows a typical application of the DMAC.

Figure 2-11 DMAC Typical Application Diagram

# 2.7.3.3 DRQ Port of Peripherals

The following tables show the source DRQ types and destination DRQ types of different ports.

Table 2-12 DMA DRQ Type

| Source DRQ Type |             | Destination D | Destination DRQ Type |  |  |

|-----------------|-------------|---------------|----------------------|--|--|

| port0           | SRAM        | port0         | SRAM                 |  |  |

| port1           | DRAM        | port1         | DRAM                 |  |  |

| port2           |             | port2         |                      |  |  |

| port3           |             | port3         |                      |  |  |

| port4           |             | port4         |                      |  |  |

| port5           |             | port5         |                      |  |  |

| port6           |             | port6         |                      |  |  |

| port7           |             | port7         |                      |  |  |

| port8           |             | port8         |                      |  |  |

| port9           |             | port9         |                      |  |  |

| port10          | NDFC        | port10        | NDFC                 |  |  |

| port11          |             | port11        |                      |  |  |

| port12          | GPADC_CTRL0 | Port12        |                      |  |  |

| port13          | GPADC_CTRL1 | port13        | CIR_TX               |  |  |

| port14          | UART0_RX    | port14        | UART0_TX             |  |  |

| port15          | UART1_RX    | port15        | UART1_TX             |  |  |

| port16          | UART2_RX    | port16        | UART2_TX             |  |  |

| port17          | UART3_RX    | port17        | UART3_TX             |  |  |

| port18          | UART4_RX    | port18        | UART4_TX             |  |  |

| port19          | UART5_RX    | port19        | UART5_TX             |  |  |

| port20          | UART6_RX    | Port20        | UART6_TX             |  |  |

| port21          | UART7_RX    | port21        | UART7_TX             |  |  |

| port22          | SPI0_RX     | port22        | SPI0_TX              |  |  |

| port23          | SPI1_RX     | port23        | SPI1_TX              |  |  |

| port24          | SPI2_RX     | port24        | SPI2_TX              |  |  |

| port25          |             | port25        |                      |  |  |

| port26          |             | port26        |                      |  |  |

| port27          |             | port27        |                      |  |  |

| port28          |             | port28        |                      |  |  |

| port29          |             | port29        |                      |  |  |

| Port30          | USB0_EP1    | Port30        | USB0_EP1             |  |  |

| Port31          | USB0_EP2    | Port31        | USB0_EP2             |  |  |

| Port32          | USB0_EP3    | Port32        | USB0_EP3             |  |  |

| Port33          | USB0_EP4    | Port33        | USB0_EP4             |  |  |

| Port34          | USB0_EP5    | Port34        | USB0_EP5             |  |  |

| Port35          |             | Port35        |                      |  |  |

| Port36          |             | Port36        |                      |  |  |

| Source DRQ Type |         | Destination DRQ Type |         |

|-----------------|---------|----------------------|---------|

| Port37          |         | Port37               |         |

| Port38          |         | Port38               |         |

| Port39          |         | Port39               |         |

| Port40          |         | Port40               |         |

| Port41          |         | Port41               |         |

| Port42          |         | Port42               | LEDC    |

| Port43          | TWI0    | Port43               | TWI0    |

| Port44          | TWI1    | Port44               | TWI1    |

| Port45          | TWI2    | Port45               | TWI2    |

| Port46          | TWI3    | Port46               | TWI3    |

| Port47          | TWI4    | Port47               | TWI4    |

| Port48          | TWI5    | Port48               | TWI5    |

| Port49          | S_TWI0  | Port49               | S_TWI0  |

| Port50          | S_TWI1  | Port50               | S_TWI1  |

| Port51          | S_UART0 | Port51               | S_UART0 |

| Port52          | S_UART1 | Port52               | S_UART1 |

| Port53          | S_SPI0  | Port53               | S_SPI0  |

Table 2-13 DMA DRQ Type of MCU\_DMAC

| Source DRQ Type |             | Destination DRQ Type |             |

|-----------------|-------------|----------------------|-------------|

| port0           | SRAM        | port0                | SRAM        |

| port1           | DRAM        | port1                | DRAM        |

| port2           | OWA         | port2                | OWA         |

| port3           | I2S0_RX     | port3                | I2S0_TX     |

| port4           | I2S1_RX     | port4                | I2S1_TX     |

| port5           | I2S2_RX     | port5                | I2S2_TX     |

| port6           | I2S3_RX     | port6                | I2S3_TX     |

| port7           | AUDIO_CODEC | port7                | AUDIO_CODEC |

| port8           | DMIC        | port8                |             |

| port9           | S_TWI0      | port9                | S_TWI0      |

| port10          | S_TWI1      | port10               | S_TWI1      |

| port11          | S_UART0     | port11               | S_UART0     |

| port12          | S_UART1     | port12               | S_UART1     |

| Port13          | S_SPI0      | Port13               | S_SPI0      |

| Port14          | S_TWI2      | Port14               | S_TWI2      |

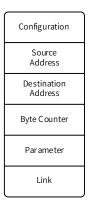

# 2.7.3.4 DMA Descriptor

The DMAC descriptor is the configuration information of DMA transfer that decides the DMA working mode. Each descriptor includes 6 words: Configuration, Source Address, Destination

Address, Byte Counter, Parameter, and Link. The following figure shows the structure of the DMA descriptor.

Figure 2-12 DMA Descriptor

- **Configuration**: Configure the following information.

- DRQ type: DRQ type of the source and destination devices.

- Address counting mode: For both the source and destination devices, there are two address counting modes: the IO mode and linear mode. The IO mode is for IO devices whose address is fixed during the data transfer and the linear mode is for the memory whose address is increasing during the data transfer.

- Transferred block length: How many times can non-memory peripherals transfer in a valid DRQ. The block length supports 1 time, 4 times, 8 times, and 16 times.

- Transferred data width: The data width of operating the non-memory peripherals. The data width supports 8 bits, 16 bits, and 32 bits.

The configuration supports BMODE mode. The BMODE is used in the following scenario: the source is an IO device, and the destination is a memory device. Setting the BMODE mode can limit the amount of block data transferred in DMA block transmission to the amount of data transferred when the DRQ threshold of the source IO device is 1.

- Source Address: Configure the address of the source device.

- **Destination Address:** Configure the address of the destination device.

DMA reads data from the source address and then writes data to the destination address.

Both the DMA source and destination addresses have 34 bits. In the descriptor, because there are only 32 bits in the Source/Destination Address field, another 2 bits are stored in the Parameter field.

The following table shows the details of the related fields in the descriptor.

Table 2-14 Source/Destination Address Distribution

| Descriptor<br>Group    | Bit   | Description                                                                                                                                                                                                                                  |  |  |

|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Source<br>Address      | 31:0  | DMA transfers the lower 32 bits of the 34-bit source address                                                                                                                                                                                 |  |  |

| Destination<br>Address | 31:0  | DMA transfers the lower 32 bits of the 34-bit destination address                                                                                                                                                                            |  |  |

|                        | 31    | TIMEOUT Enable TIMEOUT only can be enabled in BMODE and IOspeed should be disabled when using this function.                                                                                                                                 |  |  |

|                        | 30:29 | TIMEOUT Configuration 00: Not use sub-functions 01: Generate an interrupt and suspend the transmission after                                                                                                                                 |  |  |

|                        |       | timeout. 10: Generate an interrupt and end the transmission after timeout. 11: Generate an interrupt and skip to the next descriptor after timeout.                                                                                          |  |  |

| Parameter              | 28:20 | TIMEOUT Configuration Timer time of channels.                                                                                                                                                                                                |  |  |

|                        | 19:18 | DMA transfers the higher 2 bits of the 34-bit destination address                                                                                                                                                                            |  |  |

|                        | 17:16 | DMA transfers the high 2 bits of the 34-bit source address                                                                                                                                                                                   |  |  |

|                        | 15:9  | Reserved                                                                                                                                                                                                                                     |  |  |

|                        | 8     | I/O Speed Mode Enable If this bit is enabled, DMA will transmit the data of the I/O device from the source device or the destination device, or both of them at a faster speed.  Note: IOspeed and BMODE cannot be enabled at the same time. |  |  |

|                        | 7:0   | Wait Clock Cycles Set the waiting time in DRQ mode                                                                                                                                                                                           |  |  |

| Link                   | 31:2  | The address of the next group descriptor, the lower 30 bits of the word address                                                                                                                                                              |  |  |

| Link                   | 1:0   | The address of the next group descriptor, the higher 2 bits of the word address                                                                                                                                                              |  |  |

From the above table, you can get:

$Real\ DMA\ source\ address\ (in\ byte\ mode) = \{Parameter\ [17:16],\ Source\ Address\ [31:0]\};$

$Real\,DMA\,destination\,address\,(in\,byte\,mode) = \{Parameter\,[19:18], Destination\,Address\,[31:0]\};$

Real link address (in byte mode) = {Link [1:0], Link [31:2], 2'b00}.

• **Byte counter**: Configure the data amount of a package. The maximum value is (2^25-1) bytes. If the data amount of the package reaches the maximum value, even if DRQ is valid, the DMA will stop the current transfer.

• Parameter: Configure the interval between the data block. The parameter is valid for non-memory peripherals. When DMA detects that the DRQ is high, the DMA transfers the data block and ignores the status changes of the DRQ until the data transfer finishes. After that, the DMA waits for certain clock cycles (WAIT\_CYC) and executes the next DRQ detection. In addition, the Parameter is responsible for enabling and configuring TIMEOUT. In the case that the source device is an I/O device and the destination device is a memory device, the waiting time of a DRQ signal triggered by the source device can be set when TIMEOUT is enabled. When time is out, an interrupt signal of TIMEOUT will be generated by DMA. There are three subfunctions of TIMEOUT to be enabled (TIMEOUT will only generate interrupts if they are disabled): suspend the transmission of the current channel after an interrupt is generated; end the transmission of the current channel after an interrupt is generated; skip to the next descriptor for transmission after an interrupt is generated. (TIMEOUT only can be enabled in BMODE.)

The Parameter also configures whether the IOspeed is enabled or not. If IOspeed is enabled, DMA will transmit the data of the I/O device from the source device or the destination device, or both of them at a faster speed. The larger block indicates a faster speed. However, when the block is 1, the speed won't change a lot even if the IO speed is enabled.

• **Link**: If the value of the link is 0xFFFFF800, the current package is at the end of the linked list. The DMAC will stop the data transfer after transferring the package; otherwise, the value of the link is considered as the descriptor address of the next package.

No.1 No.(N-1) No.N No.2 Package Package Package Package (6 words) (6 words) (6 words) (6 words) Configuration Configuration Configuration Configuration Source Source Source Source Address Address Address Address Destination Destination Destination Destination Address Address Address Address Byte Counter Byte Counter Byte Counter Byte Counter Parameter Parameter Parameter Parameter Link Link Link 0xFFFFF800

Figure 2-13 DMA Chain Transfer

### 2.7.3.5 Interrupts

There are four kinds of DMA interrupts: the half package interrupt, package end interrupt, and queue end interrupt.

Half package interrupt

When enabled, the DMAC sends out a half package interrupt after transferring half of a package.

Package end interrupt

When enabled, the DMAC sends out a package end interrupt after transferring a complete package.

• Queue end interrupt

When enabled, the DMAC sends out a queue end interrupt after transferring a complete queue.

• Timeout interrupt

When TIMEOUT is enabled, DMA will generate a timeout interrupt after timeout.

Notice that when CPU does not respond to the interrupts timely, or two DMA interrupts are generated very closely, the later interrupt may override the former one. That is, from the perspective of the CPU, the DMAC has only a system interrupt source.

## 2.7.3.6 Clock Gating

The DMA\_CLK\_GATE module is a hardware module for controlling the clock gating automatically. It provides clock sources for sub-modules in DMAC and the module local circuits.

The DMA\_CLK\_GATE module consists of two parts: the channel clock gate and the common clock gate.

Channel clock gate: Controls the DMA clock of the DMA channels. When the system accesses the register of the current DMA channel and the DMA channel is enabled, the channel clock gate automatically opens the DMA clock. With a 16-HCLK-cycle delay after the system finishes accessing the register or the DMA data transfer is completed, the channel clock gate automatically closes the DMA clock. Also, the clock for the related circuits, such as for the channel control and FIFO control modules, will be closed.

**Common clock gate**: Controls the clocks of the DMA common circuits. The common circuits include the common circuit of the FIFO control module, MPORT module, and MBUS. When all the DMA channels are disabled, the common clock gate automatically closes the clocks for the above circuits.

The DMA clock gating can support all the functions stated above or not by software.

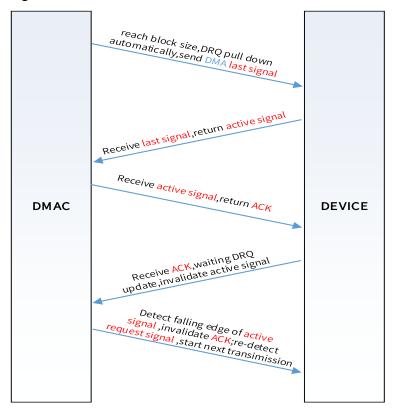

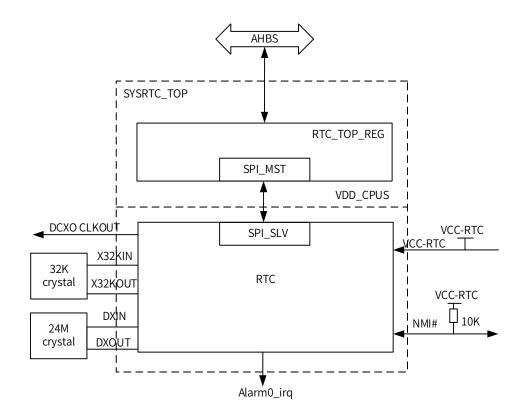

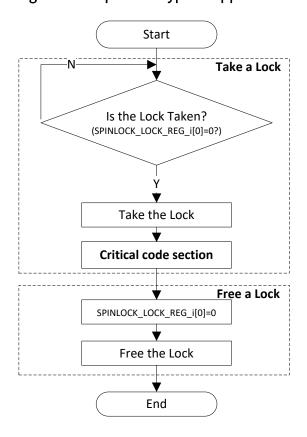

### 2.7.3.7 Transfer Mode