Глава 5. Память - Memory

Раздел 5.2. Контроллер Nand Flash (NDFC) - Nand Flash Controller(NDFC)

5.2. Контроллер Nand Flash (NDFC)

5.2.1. Обзор

NDFC - это контроллер флэш-памяти NAND, который поддерживает всю флэш-память NAND, доступную на рынке. Флеш-память нового типа может поддерживаться путем изменения конфигурации программного обеспечения. Код исправления ошибок на лету (ECC) встроен в NDFC для повышения надежности. Реализован BCH, который может обнаруживать и исправлять до 80 ошибок на 1024 байта данных. Встроенная схема ECC и проверки четности NDFC освобождает CPU для других задач. Функцию ECC можно отключить программно. Данные могут быть переданы с помощью прямого доступа к памяти или методом ввода-вывода с отображением памяти ЦП. NDFC обеспечивает автоматический контроль времени для чтения или записи внешней Flash. NDFC поддерживает надлежащую относительность для линий управляющих сигналов CLE, CE # и ALE. Существует три различных режима доступа для последовательного чтения: mode0 - для обычного последовательного доступа, mode1 - для типа EDO, а mode2 - для расширенного типа EDO. NDFC может контролировать состояние сигнальной линии R / B #. Управление блоками и управление выравниванием износа реализовано программно. NDFC имеет следующие особенности:5.2.2. Блок-схема

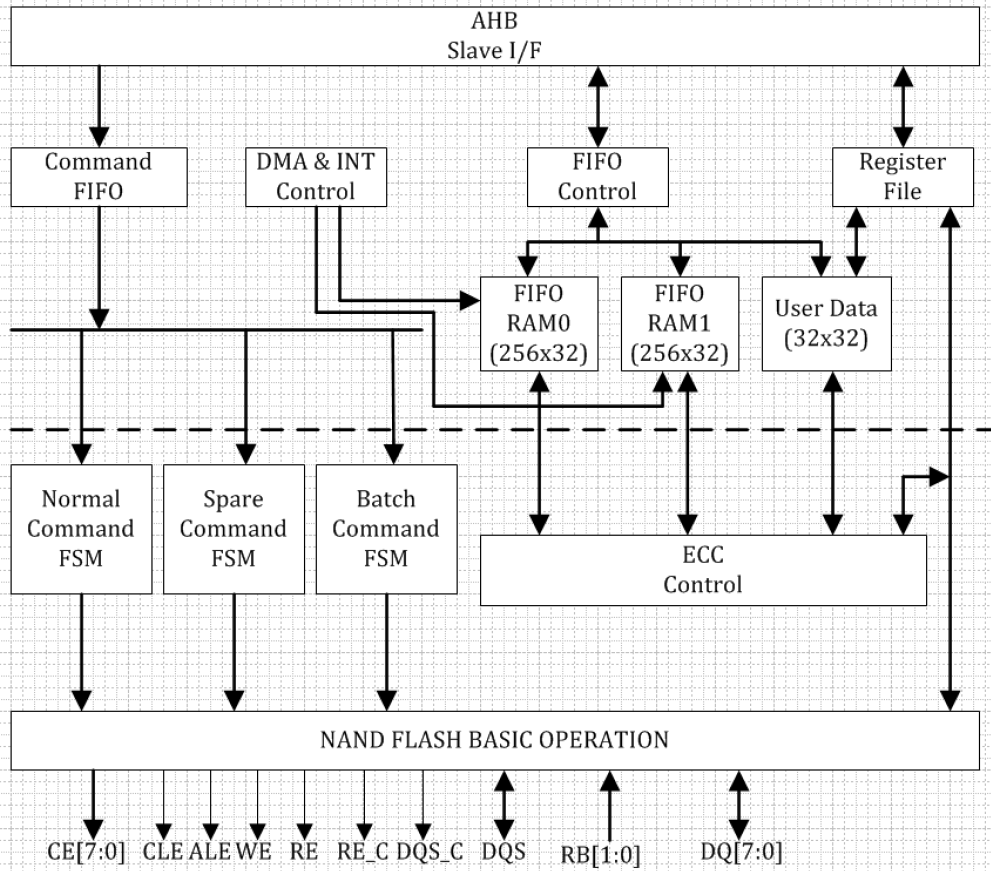

Блок-схема NDFC показана ниже.

Рисунок 5-1. Блок-схема NDFC.

5.2.3. Операции и функциональное описание

5.2.3.1

Внешние сигналы

В Таблице 5-1 описаны внешние сигналы NDFC. DQ0 ~ DQ7 и DQS - это двунаправленный ввод / вывод. WE, ALE, CLE, CE, RE - выходной контакт, RB - входной контакт. Вывод RB в устройстве NAND представляет собой драйвер с открытым стоком, для которого необходим подтягивающий резистор.5.2.3.2

Источники часов

Чтобы обеспечить эффективность ECC, механизм ECC и внутренняя логика NDFC используют разные часы. Тактовая частота внутренней логики NDFC задается регистром тактовой частоты NAND_0, тактовая частота механизма ECC устанавливается регистром тактовой частоты NAND_1. Обратите внимание, что регистр тактовой частоты NAND_0 устанавливает внутреннюю логическую тактовую частоту NDFC, но частота внешнего устройства NAND Flash составляет половину от NDFC внутренние логические часы. То есть, если внешняя Nand Flash работает на частоте 40 МГц, тогда NDFC необходимо установить на 80 МГц. И механизм ECC, и внутренняя логика NDFC имеют пять разных источников синхронизации. Пользователи могут выбрать один из них, чтобы сделать механизм ECC или источник внутренних логических часов. В Таблице 5-2 описаны источники синхронизации NDFC. Пользователи могут увидеть CCU в главе 3.3 для информации о настройке часов, конфигурации и стробировании.Таблица 5-2. Источники тактовой частоты NDFC

Источники часов Описание

5.2.3.3

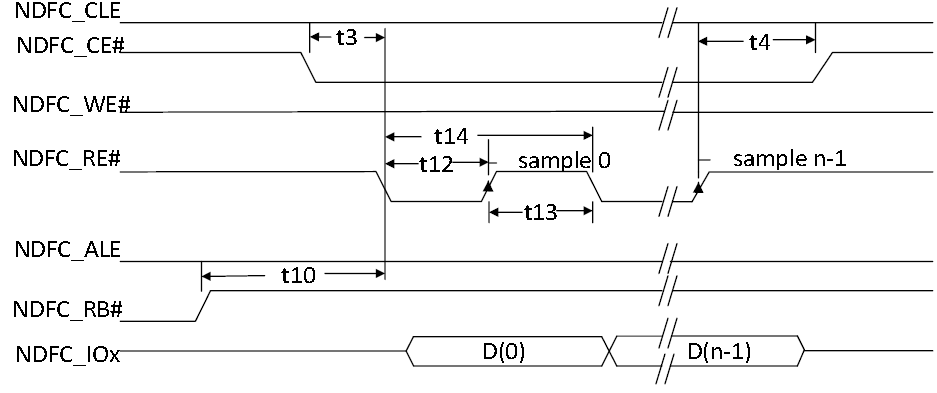

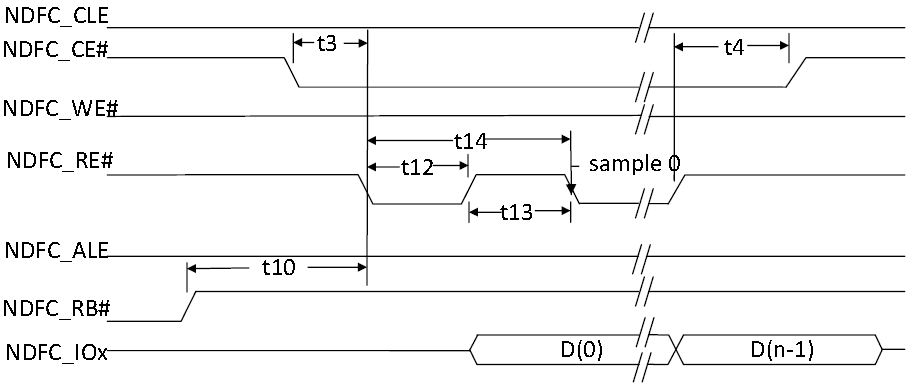

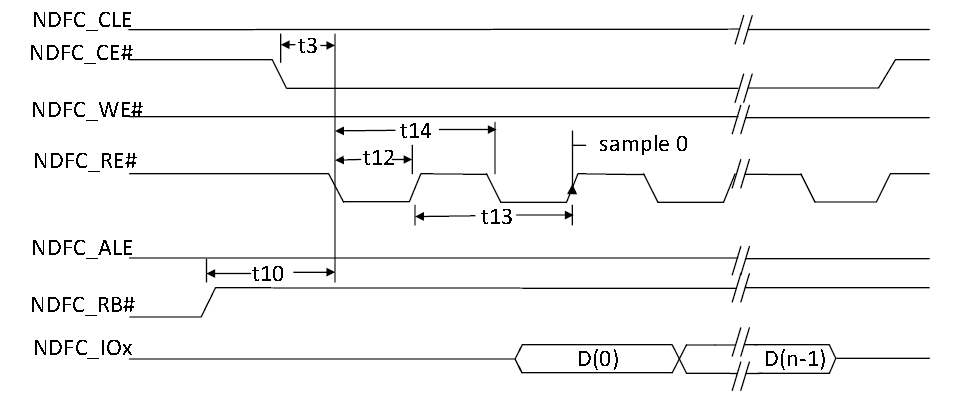

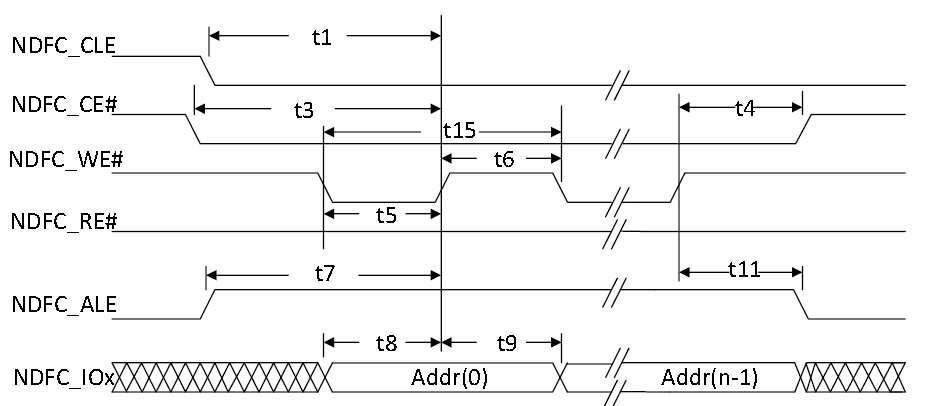

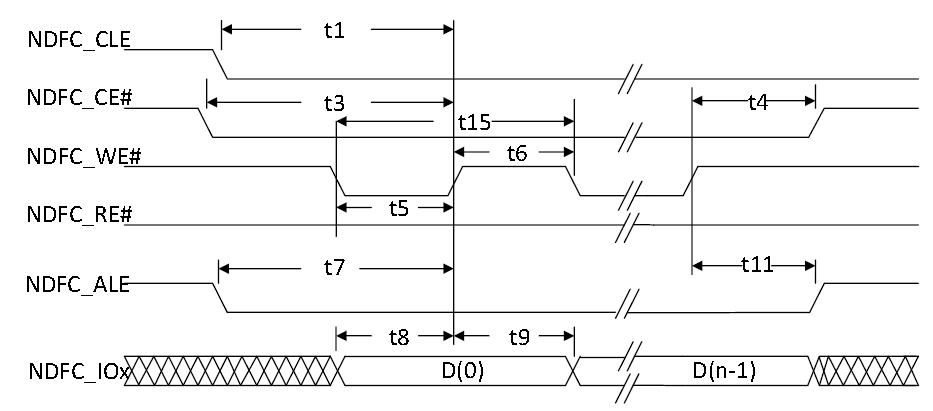

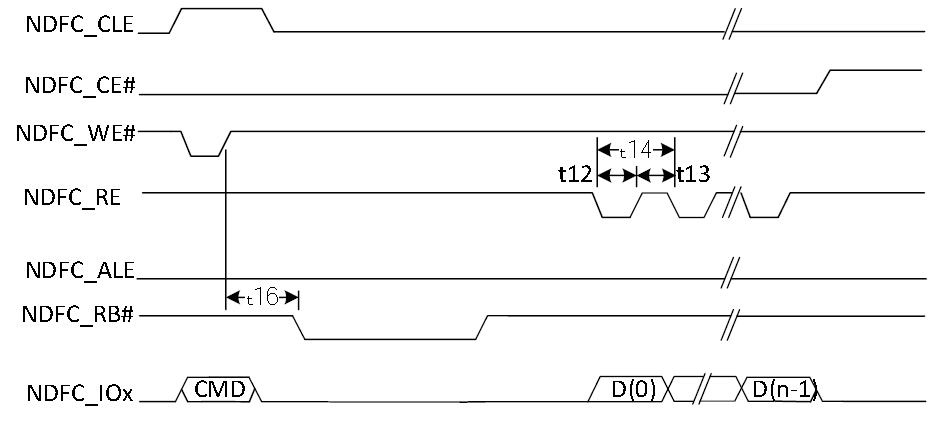

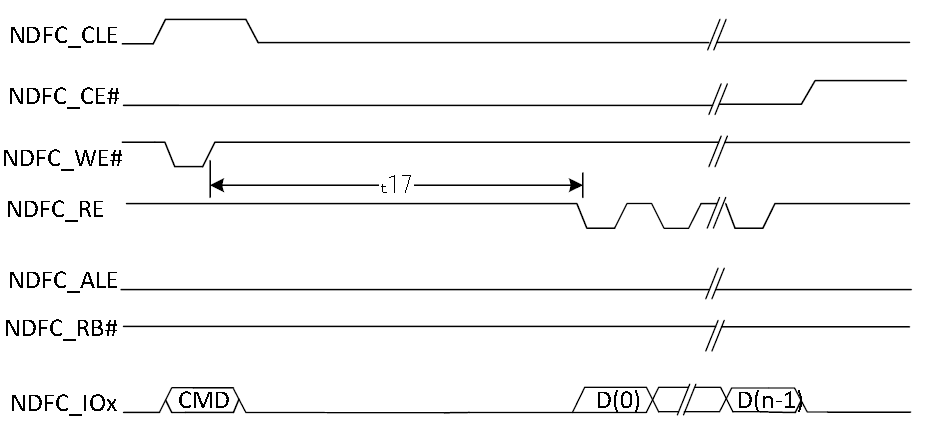

Временная диаграмма

Обычно существует два вида методов последовательного доступа. Одним из методов является традиционный метод, который выбирает данные на переднем фронте сигнальной линии NDFC_RE #. Другой тип - EDO, который выбирает данные на следующем спадающем фронте сигнальной линии NDFC_RE #.

Рисунок 5-2. Цикл обычного последовательного доступа (SAM0)

Рисунок 5-3. Последовательный доступ типа EDO после цикла чтения (SAM1)

Рисунок 5-4. Расширение режима последовательного доступа типа EDO (SAM2)

Рисунок 5-5. Цикл фиксации команды

Рисунок 5-6. Цикл фиксации адреса

Рисунок 5-7. Цикл записи данных во флэш-память.

Рисунок 5-8. Диаграмма ожидания R / B # Ready.

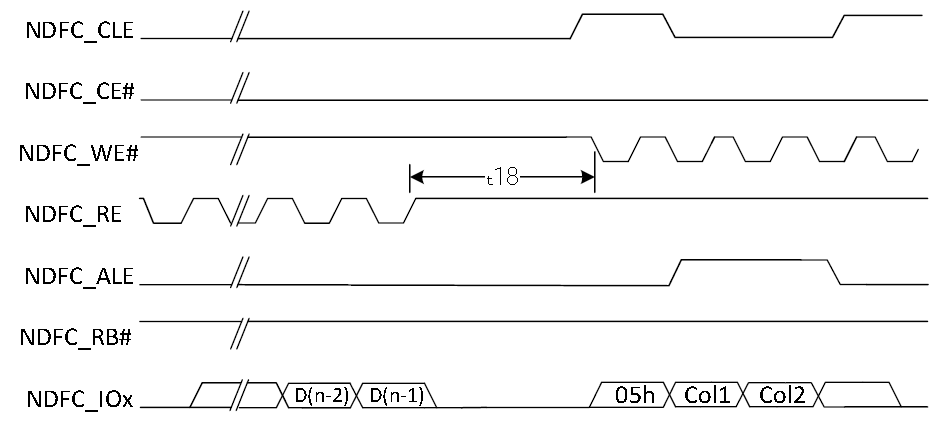

Рис. 5-9. Временная диаграмма от WE # High до RE # Low.

Рис. 5-10. Временная диаграмма RE # High - WE # Low.

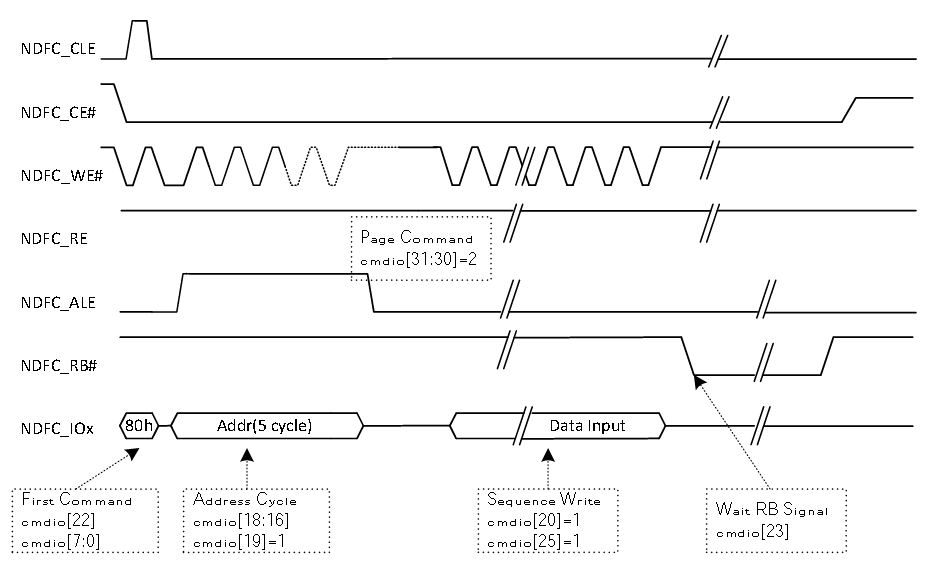

Рисунок 5-11. Временная диаграмма загрузки данных.

Список временных циклов:

ID Параметр Время (нс) Примечания

Примечание (1): T - это цикл внутренних часов

Примечание (2), (3), (4), (5): эти значения настраиваются в контроллере nand flash. Значение T_WB может быть 14 * 2T / 22 * ??2T / 30 * 2T / 38 * 2T, значение T_WHR может быть 0 * 2T / 6 * 2T / 14 * 2T / 22 * ??2T, значение T_RHW может быть 4 * 2T / 12 * 2T / 20 * 2T / 28 * 2T, значение T_ADL может быть 0 * 2T / 6 * 2T / 14 * 2T / 22 * ??2T.

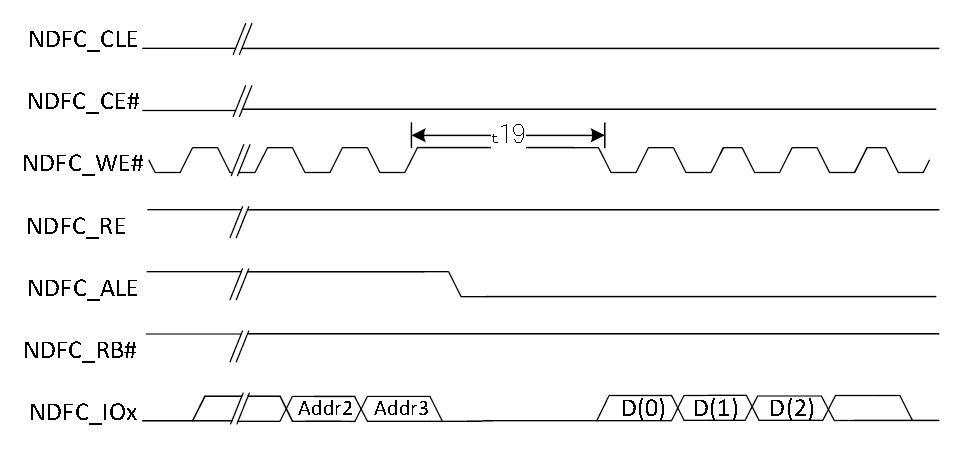

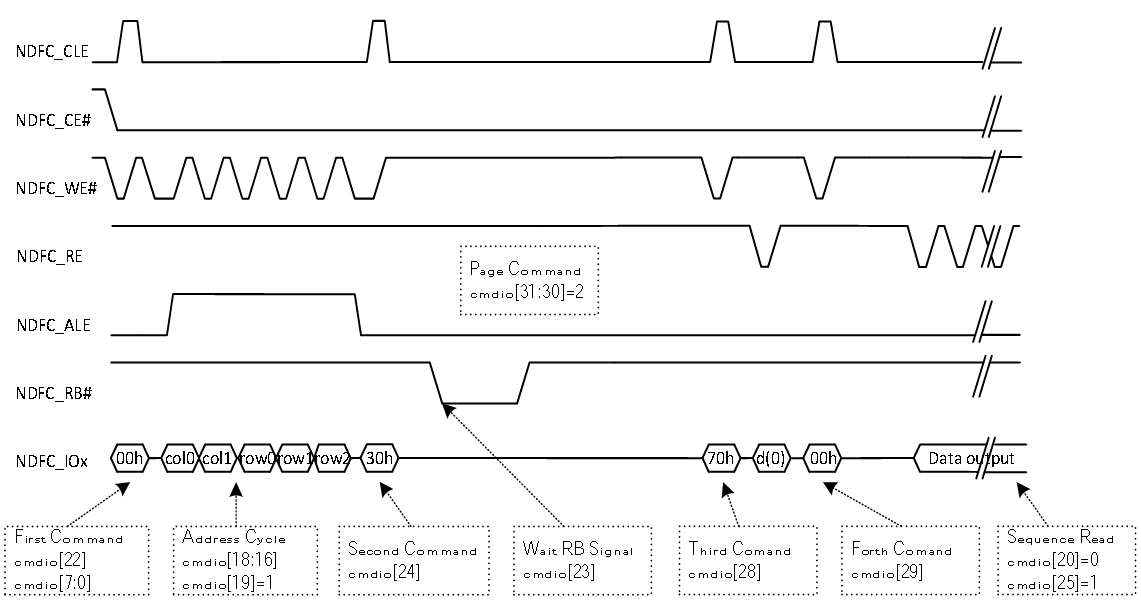

Рисунок 5-12. Диаграмма команд чтения страницы

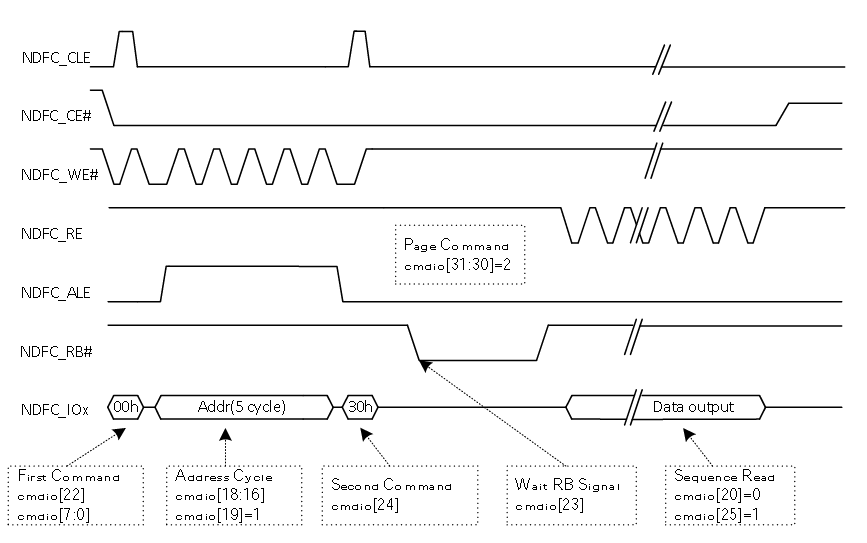

Рисунок 5-13. Диаграмма программы страницы

Рисунок 5-14. Диаграмма чтения страницы EF-NAND

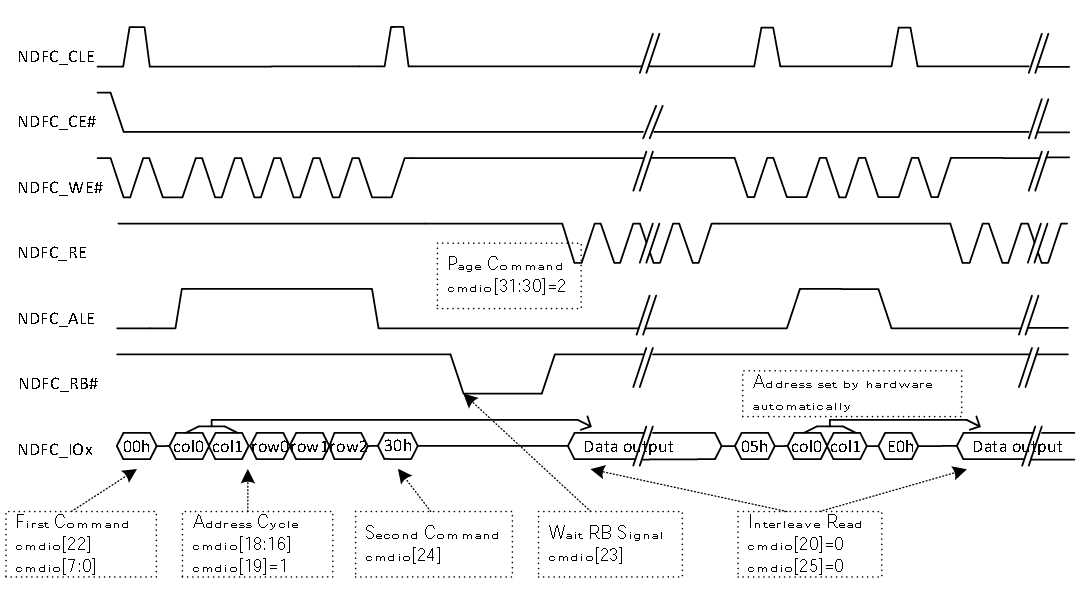

Рисунок 5-15. Диаграмма чтения страницы с чередованием 5.2.3.4.

Дескрипторы внутреннего контроллера DMA

5.2.3.4.1. Структура дескриптора

Внутренний контроллер DMA NDFC может передавать данные между DMA FIFO в NDFC и буфером DMA в памяти хоста, используя дескрипторы DMA. Дескрипторы DMA в памяти хоста с цепочечной структурой показаны на рисунке 5-16.

Рисунок 5-16. Внутренняя структура цепочки дескрипторов DMA

Начальный адрес списка дескрипторов DMA должен быть выровнен по слову (32 бита) и будет настроен как регистр базового адреса списка дескрипторов DMA NDFC. Каждый дескриптор DMA состоит из четырех слов (32-битных).5.2.3.4.2. Определение дескриптора

КонфигБит Описание

Размер

Бит Описание

Бит Описание

Следующее описание

Бит Описание

5.2.3.5

Регистр маски блока данных NDFC

ECC_DATA_BLOCK записывается или считывается через значение регистра маски блока данных NDFC. Но в реальном сценарии приложения емкость не может быть потрачена впустую, поэтому операция записи обычно не использует эту функцию, используется только операция чтения. При чтении мы разделяем режим последовательности и режим чередования на позицию сохранения user_data. Последовательный режим: user_data каждой 1K данных основной области и данные кодера ECC находятся рядом с данными основной области. Режим чередования: все данные кодировщика user_data и ECC хранятся с позиции page_size. Когда любой ECC_DATA_BLOCK на странице считывается с помощью пакетной команды (NDFC_CMD_TYPE в регистре 0x24 равен 0x10), регистр используется по-разному для режима последовательности и режима чередования. Последовательный режим может поддерживать только продолжение ECC_DATA_BLOCK, значение регистра может быть только 0x1,0x3,0x7 и т.д. Но режим чередования не имеет ограничений. Независимо от режима последовательности или режима чередования, первое чтение ECC_DATA_BLOCK используется для вычисления соответствующего адреса столбца, а адрес столбца записывается в регистры 0x14 и 0x18.5.2.3.6

Регистр расширенных функций NDFC

Бит [24] и бит [23:16] регистра используются для определения того, нужно ли заполнять свободное пространство случайными данными, за исключением достоверных данных, когда используется функция пакетной команды. В качестве примера возьмем микросхему SanDisk (SDTNQGAMA-008G): Обратитесь к спецификации чипа SanDisk, размер страницы чипа SanDisk составляет (16384 + 1280) байтов, но уровень BCH использует 40 бит / 1 КБ, если user_data составляет 32 байта, то используемое пространство составляет 1152 байта (14 * 40/8 * 16 + 32), 128 байтов (1280-1152) не записываются. Если необходимо заполнить 1 страницу, то бит [24] регистра может быть установлен в 1, а бит [23:16] записывается в 0x80, чтобы контроллер мог автоматически заполнять 128 байтов случайными данными.Примечание Убедитесь, что функция случайного выбора включена, если необходимо отправить случайные данные, то есть NDFC_RANDOM_EN регистра 0x34 равно 0x1, иначе данные заполнения не являются случайными, все равно 0.

5.2.4. Рекомендации по программированию

5.2.4.1

Инициализация Nand Flash

Флэш-память NAND инициализируется следующим образом:5.2.4.2

Стирание Nand Flash

NAND Flash стирается следующим образом:5.2.4.3

Запись Nand Flash

- Установите NDFC_CMD [NDFC_SEND_FIRST_CMD] на 1 для отправки первой команды, настройте NDFC_CMD [NDFC_DATA_TRANS, NDFC_ACCESS_DIR] на 0x3, чтобы установить направление доступа как запись;

- Установите NDFC_CMD [NDFC_SEND_ADR] на 1, чтобы включить адрес передачи, настройте NDFC_CMD [NDFC_ADR_NUM], чтобы установить номер адреса для передачи, запишите адрес блока, который будет работать, в NDFC_ADDR_LOW и NDFC_ADDR_HIGH;

- Установите NDFC_CMD [NDFC_CMD_LOW_BYTE] на 0x80 для отправки команды программы страницы.

5.2.4.4

Чтение Nand Flash

- Настройте NDFC_CMD [NDFC_SEND_FIRST_CMD] на 1 для отправки первой команды; Настройте NDFC_CMD [NDFC_ACCESS_DIR] на 0, чтобы установить направление доступа как чтение;

- Установите NDFC_CMD [NDFC_SEND_ADR] на 1, чтобы включить адрес передачи, настройте NDFC_CMD [NDFC_ADR_NUM], чтобы установить номер адреса для передачи, запишите адрес блока, который будет работать, в NDFC_ADDR_LOW и NDFC_ADDR_HIGH;

- Установите NDFC_CMD [NDFC_CMD_LOW_BYTE] на 0x00 для отправки команды чтения страницы.