|

Глава 5. Память - Memory

Раздел 5.3. Хост-контроллер SD / MMC (SMHC) - SD/MMC Host Controller(SMHC)

5.3. Хост-контроллер SD / MMC (SMHC)

5.3.1. Обзор Хост-контроллер SD-MMC (SMHC) управляет операциями чтения / записи на защищенной цифровой (SD) карте и мультимедийной карте (MMC) и поддерживает различные расширенные устройства на основе протокола защищенного цифрового ввода / вывода (SDIO). H616 предоставляет три интерфейса SMHC для управления SD-картой, MMC и устройством SDIO. SMHC имеет следующие особенности: Поддерживает загрузку eMMC Поддерживает сигнал завершения команды и прерывание для хост-процессора, а также функцию отключения сигнала завершения команды SMHC0 поддерживает SD (версии от 1.0 до 3.0), 4-битную ширину шины

- Режим SDR 50 МГц @ 3.3 В IO pad

- Режим DDR 50 МГц @ 3.3V IO pad

- Режим SDR 150 МГц @ 1,8 В IO pad SMHC1 поддерживает SDIO (версии от 1.1 до 3.0), 4-битную ширину шины

- Режим SDR 50 МГц @ 3.3 В IO pad

- Режим DDR 50 МГц @ 3.3V IO pad

- Режим SDR 150 МГц @ 1,8 В IO pad SMHC2 поддерживает MMC (версии от 3.3 до 5.0), 8-битную ширину шины

- Режим SDR 50 МГц @ 3.3 В IO pad

- Режим DDR 50 МГц @ 3.3V IO pad

- Режим SDR 150 МГц @ 1,8 В IO pad

- Режим DDR 100 МГц @ 1,8 В IO pad Аппаратная генерация CRC и обнаружение ошибок Программируемая скорость передачи Управление подтягиванием хоста Поддерживает прерывание SDIO в 1-битном и 4-битном режимах Размер блока от 1 до 65535 байт Внутренний контроллер DMA на основе дескрипторов Внутренний FIFO 1 КБ для передачи данных SMHC0 осуществляет преобразование с 3,3 В до 1,8 В, независимое питание LDO не требуется

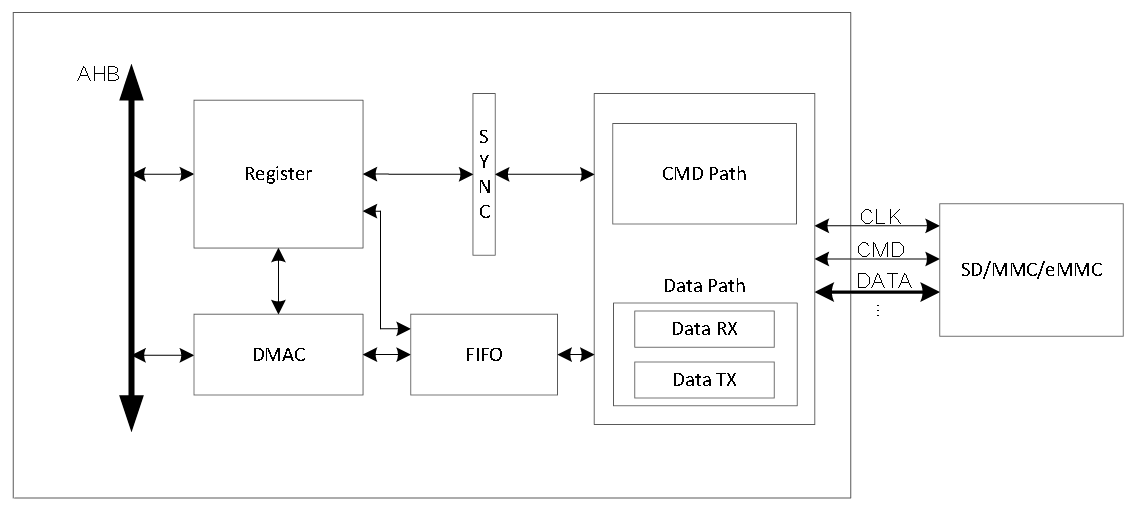

5.3.2. Блок-схема На рисунке 5-17 показана блок-схема SMHC. Рисунок 5-17. Блок-схема SMHC .

5.3.3. Операции и функциональные описания

5.3.3.1Внешние сигналы Таблица 5-1. Внешние сигналы SMHC Имя порта Ширина Тип Описание SDC0_CLK 1 O Выход часов для карты SD / TF SDC0_CMD 1 I / O, линия OD CMD для SD / TF карты SDC0_D [i] (i = 0 ~ 3) 4 строки ввода / вывода для карты SD / TF SDC1_CLK 1 O Выход часов для SDIO Wi-Fi SDC1_CMD 1 I / O, линия OD CMD для SDIO Wi-Fi SDC1_D [i] (i = 0 ~ 3) 4 линии ввода-вывода для SDIO Wi-Fi SDC2_CLK 1 O Тактовый выход для MMC SDC2_CMD 1 I / O, OD CMD линия для MMC SDC2_D [i] (i = 0 ~ 7) 8 линий ввода / вывода для MMC SDC2_RST 1 O Сигнал сброса для MMC SDC2_DS 1 I Строб данных для MMC

5.3.3.2Источники синхроимпульсов Каждый SMHC получает три разных тактовых сигнала. Пользователь может выбрать один из них для создания тактового сигнала SMHC. В Таблице 5-2 описаны источники тактовой частоты SMHC. Пользователи могут увидеть CCU в главе 3.3 для информации о настройке часов, конфигурации и стробировании. Таблица 5-4. Источники тактовых сигналов SMHC OSC24M Кристалл 24 МГц PLL_PERI0 (2X) Периферийные часы, значение по умолчанию - 1,2 ГГц. PLL_PERI1 (2X) Периферийные часы, значение по умолчанию - 1,2 ГГц

5.3.3.3Временная диаграмма См. Относительные характеристики: Спецификация физического уровня, окончательная версия 3.00 Спецификация SDIO версии 2.00 Мультимедийные карты (MMC - версия 4.2) Стандарт JEDEC - JESD84-44, Стандарт продукта для карт встроенной мультимедийной карты (eMMC) Стандарт JEDEC - JESD84-B45, электрический стандарт встроенной мультимедийной карты (eMMC) (устройство 4.5) Стандарт JEDEC - JESD84-B50, Электрический стандарт для встроенной мультимедийной карты (eMMC) (5.0)

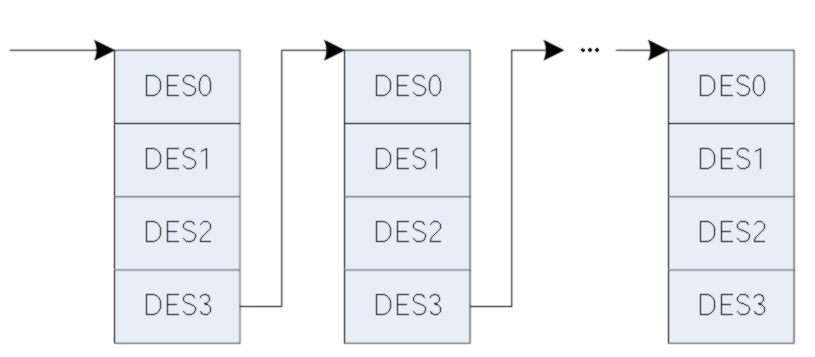

5.3.3.4Описание внутреннего контроллера прямого доступа DMA SMHC имеет внутренний контроллер DMA (IDMAC) для передачи данных между памятью хоста и портом SMHC. С помощью дескриптора IDMAC может эффективно перемещать данные из источника в пункт назначения, автоматически загружая следующие аргументы передачи DMA, которые требуют меньшего вмешательства процессора. Перед передачей данных в IDMAC драйвер хоста должен создать список дескрипторов, настроить аргументы каждой передачи DMA, затем запустить дескриптор и запустить DMA. IDMAC имеет контроллер прерываний, когда он включен, он может прерывать работу HOST CPU в таких ситуациях, как завершение передачи данных или возникновение некоторых ошибок. 1. Структура дескриптора IDMAC IDMAC использует дескриптор с цепочкой, и каждый дескриптор указывает на уникальный буфер и следующий дескриптор.

Рисунок 5-18. Схема структуры дескриптора IDMAC На этом рисунке показаны внутренние форматы дескриптора. Адрес дескриптора должен быть выровнен по ширине шины, используемой для 32-битных шин. Каждый дескриптор содержит 16 байтов управляющей информации и информации о состоянии. DES0 - это нотация, используемая для обозначения битов [31: 0], DES1 для обозначения [63:32] битов, DES2 для обозначения [95:64] битов и DES3 для обозначения [127: 96] битов в дескрипторе. 2. DES0 Определение Бит Имя Дескриптор 31 HOLD DES_OWN_FLAG Когда установлен, этот бит указывает, что дескриптор принадлежит IDMAC. Когда этот бит сброшен, это указывает, что дескриптор принадлежит хост. Этот бит сбрасывается после завершения передачи. 30 ОШИБКА ERR_FLAG Если при передаче произошла какая-то ошибка, этот бит будет установлен. 29: 5 / / 4 Флаг цепочки CHAIM_MOD Если установлен, этот бит указывает, что второй адрес в дескрипторе адрес следующего дескриптора. Должен быть установлен 1. 3 Флаг первого DES FIRST_FLAG Если установлен, этот бит указывает, что этот дескриптор содержит первый буфер данных. В первом DES должно быть установлено значение 1. 2 Последний флаг DES LAST_FLAG Если установлен, этот бит указывает, что буферы, на которые указывает этот дескриптор - это последний буфер данных 1 Запретить прерывание по завершении CUR_TXRX_OVER_INT_DIS Если установлен, этот бит предотвращает установку бита прерывания TX / RX регистр состояния IDMAC для данных, которые заканчиваются в буфере, на который указывает этот дескриптор 0 / / 3. DES1 Определение Для SMHC0 / SMCH1: Бит Имя Дескриптор 31:16 / / 15: 0 Размер буфера BUFF_SIZE Эти биты указывают размер байта буфера данных, который должен быть кратным 4. байтов. Если это поле равно 0, DMA игнорирует этот буфер и переходит к следующему дескрипторe Для SMHC2: 31:13 / / 12: 0 Размер буфера BUFF_SIZE Эти биты указывают размер байта буфера данных, который должен быть кратным 4 байтам. Если это поле равно 0, DMA игнорирует этот буфер и переходит к следующему дескриптору. 4. DES2 Определение Бит Имя Дескриптор 31: 0 BUFF_ADDR Указатель адреса буфера Эти биты указывают физический адрес буфера данных. Для SMHC0, SMHC1 поле представляет собой адрес слова. Для SMHC2 поле представляет собой байтовый адрес. 5. DES3 Определение Бит Имя Дескриптор 31: 0 адрес следующего дескриптора NEXT_DESP_ADDR Эти биты указывают указатель на физическую память, где присутствуетследующий дескриптор . Для SMHC0, SMHC1 поле представляет собой адрес слова. Для SMHC2 поле представляет собой байтовый адрес.

5.3.3.5Калибровка цепочки задержки Цепочка задержки тактового сигнала выборки и цепочка задержки строба данных (эта цепочка есть только в SMHC2) используются для генерации задержки, чтобы обеспечить правильную синхронизацию между внутренними тактовыми импульсами / стробом данных карты и сигналами данных. Каждая цепочка задержки состоит из 64 ячеек задержки. Время задержки одной ячейки задержки можно оценить с помощью калибровки цепи задержки. Шаги по калибровке цепочки задержки следующие. Шаг 1. Включите SMHC. Чтобы откалибровать цепочку задержки с помощью рабочих регистров в SMHC, SMHC должен быть включен через регистр сброса стробирования шины SMHC и регистр тактовых импульсов SMHC0 / 1/2. Шаг 2: Настройте правильные часы для SMHC. Цепочка задержки калибровки основана на часах для SMHC от блока управления часами (CCU). Цепочка задержки калибровки является внутренней функцией SMHC и не требует устройства. Таким образом, нет необходимости включать тактовый сигнал для устройства. Рекомендуемая тактовая частота - 200 МГц. Шаг 3: Установите правильное начальное значение задержки. Запись 0xA0 в регистр управления задержкой включает включение программного обеспечения задержки (бит [7]) и устанавливает начальное значение задержки 0x20 в цепочку задержки (бит [5: 0]). Затем запишите 0x0 в регистр управления задержкой, чтобы очистить значение. Шаг 4: Запишите 0x8000 в регистр управления задержкой, чтобы начать калибровку цепочки задержки. Шаг 5: Подождите, пока не будет установлен флаг (бит 14 в регистре управления задержкой) выполненной калибровки. Количество ячеек задержки показано в бите [13: 8] в регистре управления задержкой. Время задержки, генерируемое этими ячейками задержки, почти равно такту часов SMHC. Это значение является результатом калибровки. Шаг 6: Рассчитайте время задержки одной ячейки задержки в соответствии с периодом тактового сигнала SMHC и результатом калибровки. Примечание В приведенных выше описаниях регистр управления задержкой содержит регистр управления задержкой выборки SMHC и регистр управления задержкой строба данных SMHC. Включение программного обеспечения задержки содержит включение программного обеспечения задержки выборки и программного обеспечения задержки строба данных. Цепочка задержки содержит программное обеспечение задержки выборки и программное обеспечение задержки строба данных.

5.3.4. Рекомендации по программированию

5.3.4.1Инициализация Перед обменом данными и командами между картой и SMHC необходимо инициализировать SMHC. SMHC инициализируется следующим образом. Шаг 1: Настройте регистр GPIO как функцию SMHC с помощью модуля контроллера порта; сбросить часы, записав 1 в SMHC_BGR_REG [SMHCx_RST], открыть синхронизацию, записав 1 в SMHC_BGR_REG [SMHCx_GATING]; выберите источники синхронизации и установите коэффициент деления, настроив регистр SMHCx_CLK_REG (x = 0,1,2). Шаг 2: Настройте SMHC_CTRL для сброса FIFO и контроллера, разрешения полного прерывания; сконфигурируйте SMHC_INTMASK на 0xFFCE, чтобы разрешить нормальное прерывание и аварийное прерывание из-за ошибки, а также зарегистрировать функцию прерывания. Шаг 3: Настройте SMHC_CLKDIV для открытия часов для устройства; настроить SMHC_CMD как команду изменения часов (например, 0x80202000); отправить команду обновления часов, чтобы доставить часы на устройство. Шаг 4: Настройте SMHC_CMD на обычную команду, настройте SMHC_CMDARG для установки параметра команды, настройте SMHC_CMD для установки типа ответа и т.д., После чего команда может быть отправлена. В соответствии с начальным процессом в протоколе, вы можете завершить инициализацию SMHC, отправив соответствующие команды одну за другой.

5.3.4.2Запись одного блока данных Чтобы записать отдельный блок данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать 0x82 в SMHC_IDMAC, чтобы разрешить прерывание IDMAC, настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA для определения начального адреса дескриптора DMA. Шаг 3. Если записывается 1 блок данных в сектор 1, то SMHC_BYCNT [BYTE_CNT] необходимо установить в 0x200, дескриптор устанавливается на основе размера данных; установите адрес сектора данных CMD24 (запись одного блока данных) на 0x1, запишите 0x80002758 в SMHC_CMD, отправьте команду CMD24 для записи данных в устройство. Шаг 4: проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 5: Проверьте, равен ли SMHC_IDST_REG [TX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 6: Проверьте, равен ли SMHC_RINTSTS [DTC] 1. Если да, передача данных завершена и операция записи CMD24 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность. Шаг 7. Отправьте команду CMD13, чтобы узнать, завершена ли операция записи устройства и вернуться ли в состояние ожидания. Например, устройство RCA - 0x1234, сначала установите SMHC_CMDARG на 0x12340000, запишите 0x8000014D в SMHC_CMD, перейдите к ?Шагу 4, чтобы убедиться, что передача команды завершена, затем проверьте, равен ли самый старший бит SMHC_RESP0 (ответ CMD13) 1. Если да, устройство находится в режиме ожидания status, то можно отправить следующую команду. Если нет, устройство находится в состоянии «занято», затем продолжайте посылать CMD13 для ожидания устройства в состоянии ожидания до завершения тайм-аута.

5.3.4.3Чтение одного блока данных Чтобы прочитать отдельный блок данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать SMHC_IDMAC в 0x82, чтобы разрешить прерывание IDMAC и настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA, чтобы определить начальный адрес дескриптора DMA. Шаг 3. При чтении 1 блока данных из сектора 1 необходимо установить SMHC_BYCNT [BYTE_CNT] на 0x200, дескриптор устанавливается на основе размера данных; установить адрес сектора данных команды CMD17 (чтение отдельного блока данных) на 0x1, записать 0x80002351 в SMHC_CMD, отправить команду CMD17 для чтения данных из устройства в DRAM / SRAM. Шаг 4: проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 5: Проверьте, равен ли SMHC_IDST_REG [RX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до тайм-аута, затем выйдите из процесса Шаг 6: проверьте, все ли SMHC_RINTSTS [ACD] и SMHC_RINTSTS [DTC] равны 1. Если да, передача данных завершена, передача CMD12 завершена и операция чтения CMD18 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность.

5.3.4.4Запись нескольких открытых блоков данных (CMD25 + Auto CMD12) Чтобы записать несколько открытых блоков данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать SMHC_IDMAC в 0x82, чтобы разрешить прерывание IDMAC и настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA для определения начального адреса дескриптора DMA. Шаг 3. Если записываются 3 блока данных в сектор 0, тогда SMHC_BYCNT [BYTE_CNT] необходимо установить в 0x600, дескриптор устанавливается на основе размера данных; установите адрес сектора данных команды CMD25 (запись нескольких блоков данных) на 0x0, запишите 0x80003759 в SMHC_CMD, отправьте команду CMD25 для записи данных на устройство, когда передача данных будет завершена, CMD12 будет отправлен автоматически. Шаг 4: проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 5: Проверьте, равен ли SMHC_IDST_REG [TX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 6: проверьте, все ли SMHC_RINTSTS [ACD] и SMHC_RINTSTS [DTC] равны 1. Если да, передача данных завершена, передача CMD12 завершена и операция записи CMD25 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность. Шаг 7. Отправьте команду CMD13, чтобы узнать, завершена ли операция записи устройства и вернуться ли в состояние ожидания. Например, устройство RCA - 0x1234, сначала установите SMHC_CMDARG на 0x12340000, запишите 0x8000014D в SMHC_CMD, перейдите к шагу 4, чтобы убедиться, что передача команды завершена, затем проверьте, равен ли самый старший бит SMHC_RESP0 (ответ CMD13) 1. Если да, устройство находится в режиме ожидания. status, то можно отправить следующую команду. Если нет, устройство находится в состоянии «занято», затем продолжайте посылать CMD13 для ожидания устройства в состоянии ожидания до завершения тайм-аута.

5.3.4.5Чтение нескольких открытых блоков данных (CMD18 + Auto CMD12) Чтобы прочитать несколько открытых блоков данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать SMHC_IDMAC в 0x82, чтобы разрешить прерывание IDMAC и настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA для определения начального адреса дескриптора DMA. Шаг 3. При чтении 3 блоков данных из сектора 0 необходимо установить SMHC_BYCNT [BYTE_CNT] на 0x600, дескриптор устанавливается на основе размера данных; установите адрес сектора данных команды CMD18 (чтение нескольких блоков данных) на 0x0, запишите 0x80003352 в SMHC_CMD, отправьте команду CMD18 для чтения данных на устройство, когда передача данных будет завершена, CMD12 будет отправлен автоматически. Шаг 4: проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 5: Проверьте, равен ли SMHC_IDST_REG [RX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 6: проверьте, все ли SMHC_RINTSTS [ACD] и SMHC_RINTSTS [DTC] равны 1. Если да, передача данных завершена, передача CMD12 завершена и операция чтения CMD18 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность.

5.3.4.6Запись предварительно определенных нескольких блоков данных (CMD23 + CMD25) Чтобы записать несколько заранее определенных блоков данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать SMHC_IDMAC в 0x82, чтобы разрешить прерывание IDMAC и настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA, чтобы определить начальный адрес дескриптора DMA. Шаг 3. При записи 3 блоков данных установите для SMHC_CMDARG значение 0x3, чтобы обеспечить работу с номером блока, запишите 0x80000157 в SMHC_CMD для отправки команды CMD23. Проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 4: SMHC_BYCNT [BYTE_CNT] необходимо установить в 0x600, дескриптор устанавливается на основе размера данных; установите адрес сектора данных команды CMD25 (запись нескольких блоков данных) на 0x0, запишите 0x80002759 в SMHC_CMD, отправьте команду CMD25 для записи данных в устройство. Шаг 5: Проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 6. Проверьте, равен ли SMHC_IDST_REG [TX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 7. Проверьте, равен ли SMHC_RINTSTS [DTC] 1. Если да, то передача данных завершена и операция записи CMD25 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность. Шаг 8: Отправьте команду CMD13, чтобы узнать, завершена ли операция записи устройства и вернуться ли в состояние ожидания. Например, устройство RCA - 0x1234, сначала установите SMHC_CMDARG на 0x12340000, запишите 0x8000014D в SMHC_CMD, перейдите к ?Шагу 4, чтобы убедиться, что передача команды завершена, затем проверьте, равен ли самый старший бит SMHC_RESP0 (ответ CMD13) 1. Если да, устройство находится в режиме ожидания. status, то можно отправить следующую команду. Если нет, устройство находится в состоянии «занято», затем продолжайте посылать CMD13 для ожидания устройства в состоянии ожидания до завершения тайм-аута.

5.3.4.7Чтение предварительно определенных нескольких блоков данных (CMD23 + CMD18) Чтобы прочитать несколько заранее определенных блоков данных, выполните следующие действия: Шаг 1: Запишите 0x1 в SMHC_CTRL [DMA_RST] для сброса внутреннего контроллера DMA; записать SMHC_IDMAC в 0x82, чтобы разрешить прерывание IDMAC и настроить передачу пакетов главного AHB; настройте SMHC_IDIE, чтобы разрешить прерывание передачи, прерывание приема и аварийное прерывание. Шаг 2: Настройте SMHC_FIFOTH для определения размера пакета, уровня запуска TX / RX. Например, если SMHC_FIFOTH настроен как 0x300F00F0, что указывает, что размер пакета равен 16, TX_TL равен 15, RX_TL равен 240. Настройте SMHC_DLBA, чтобы определить начальный адрес дескриптора DMA. Шаг 3: при чтении 3 блоков данных, установка SMHC_CMDARG на 0x3, чтобы гарантировать работу номера блока, запись 0x80000157 в SMHC_CMD для отправки команды CMD23. Проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 4: SMHC_BYCNT [BYTE_CNT] необходимо установить в 0x600, дескриптор устанавливается на основе размера данных; установить адрес сектора данных CMD18 (чтение нескольких блоков данных) на 0x0, записать 0x80002352 в SMHC_CMD, отправить команду CMD18 для чтения данных из устройства в DRAM / SRAM. Шаг 5: Проверьте, равен ли SMHC_RINTSTS [CC] 1. Если да, команда отправляется успешно; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 6. Проверьте, равен ли SMHC_IDST_REG [TX_INT] 1. Если да, запись данных DMA завершена, затем запишите 0x337 в SMHC_IDST_REG, чтобы сбросить флаг прерывания; если нет, продолжайте ждать до истечения времени ожидания, затем выйдите из процесса. Шаг 7. Проверьте, равен ли SMHC_RINTSTS [DTC] 1. Если да, то передача данных завершена и операция записи CMD18 завершена. Если нет, то есть отклонение от нормы. Прочтите SMHC_RINTSTS, SMHC_STATUS, чтобы запросить существующую неисправность.

|

|