|

Глава 3. Система - System

Раздел 3.9. Прямой доступ к памяти - Direct Memory Access (DMA)

3.9. DMA

3.9.1. Обзор Прямой доступ к памяти (DMA) используется для передачи данных между периферийным устройством и памятью, между периферийными устройствами или между памятью. DMA - это операция высокоскоростной передачи данных, уменьшающая ресурсы ЦП. DMA имеет следующие особенности: 16 каналов DMA Обеспечивает 32 периферийных запроса DMA для чтения данных и 32 периферийных запроса DMA для записи данных Перенос со связанным списком Программируемая 8-, 16-, 32-, 64-битная ширина данных Программируемая длина пакета DMA Ответ DRQ включает режим ожидания и режим квитирования Устройства памяти поддерживают невыровненное преобразование Канал DMA поддерживает функцию паузы

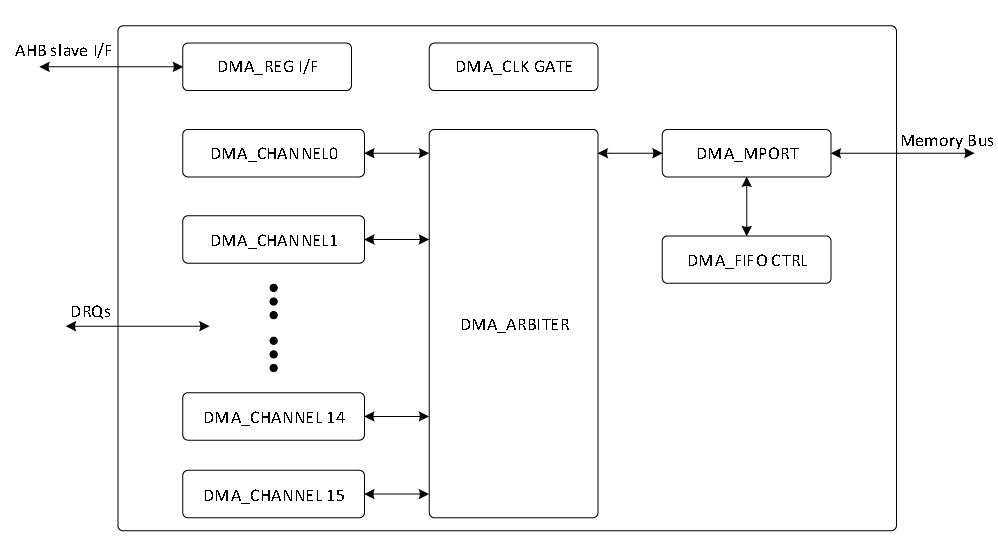

3.9.2. Блок-схема На следующем рисунке показана блок-схема DMA. Рисунок 3-17. Блок-схема DMA. DMA_ARBITER: Арбитражное требование чтения / записи DMA для каждого канала и преобразование в требования чтения / записи каждого порта. DMA_CHANNEL: механизм преобразования DMA. Каждый канал независим. Приоритеты каналов DMA используют механизм опроса. Когда запросы DMA от двух периферийных устройств действительны одновременно, если DMA_ARBITER не находится в состоянии ожидания, следующий канал текущего канала имеет более высокий приоритет; если DMA_ARBITER неактивен, канал 0 имеет наивысший приоритет, а канал 15 - самый низкий. DMA_MPORT: получить требование чтения / записи DMA_ARBITER и преобразовать в соответствующий доступ MBUS. DMA_FIFOCTL: внутренний модуль управления ячейкой FIFO. DMA_REGIF: модуль общего регистра, в основном используемый для разрешения запроса AHB1. DMA_CLKGATE: Аппаратный модуль управления автоматическим синхронизацией. DMA объединяет 16 независимых каналов DMA. Когда канал DMA запускается, DMA получает дескриптор DMA посредством DMA_DESC_ADDR_REG для использования для информации конфигурации текущей передачи пакета DMA, и DMA может передавать данные между указанными периферийными устройствами через информацию конфигурации. Когда передача пакета завершена, DMA определяет, завершена ли передача текущего канала или продолжает получать / передавать дескриптор следующего пакета через связанную информацию в дескрипторе. Когда связанная адресная информация дескриптора указывает, что передача текущего канала завершена, DMA закроет цепную передачу и канал.

3.9.3. Операции и функциональные описания

3.9.3.1Часы и сброс DMA находится на AHB1. Часы AHB1 влияют на эффективность передачи DMA.

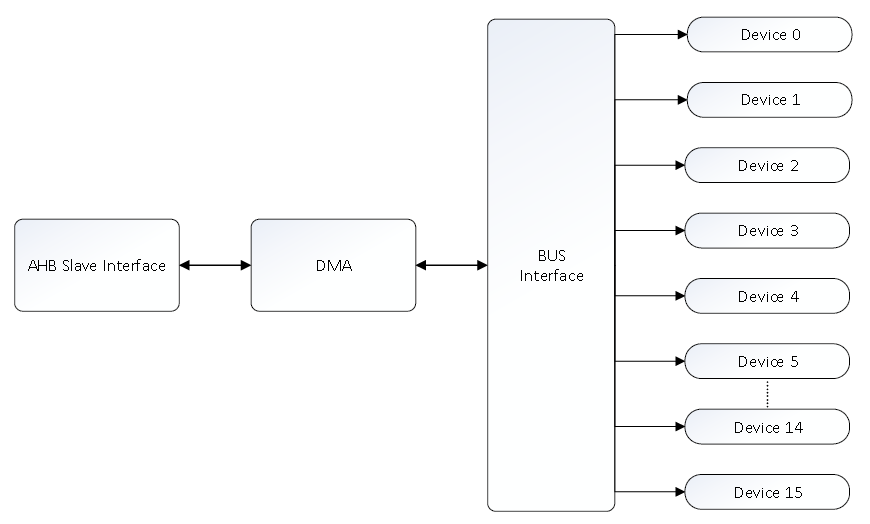

3.9.3.2Типичное применение Рисунок 3-18. Схема типового применения DMA

3.9.3.3DRQ Type Таблица 3-7. Таблица DMA DRQ Источник DRQ Тип | Целевой Тип DRQ

port0 SRAM port0 SRAM port1 DRAM port1 DRAM port2 port2 OWA port3 AHUB_drqr0 port3 AHUB_drqt0 port4 AHUB_drqr1 port4 AHUB_drqt1 port5 AHUB_drqr2 port5 AHUB_drqt2 port6 port6 Audio Codec port7 DMIC port7 port8 port8 port9 port9 port10 NAND0 port10 NAND0 port11 port11 port12 port12 port13 port13 port14 UART0_RX port14 UART0_TX port15 UART1_RX port15 UART1_TX port16 UART2_RX port16 UART2_TX port17 UART3_RX port17 UART3_TX port18 UART4_RX port18 UART4_TX port19 UART5_RX port19 UART5_TX port20 port20 port21 port21 port22 SPI0_RX port22 SPI0_TX port23 SPI1_RX port23 SPI1_TX port24 port24 port25 port25 port26 port26 port27 port27 port28 port28 port29 port29 Port30 OTG_EP1 Port30 OTG_EP1 Port31 OTG_EP2 Port31 OTG_EP2 Port32 OTG_EP3 Port32 OTG_EP3 Port33 OTG_EP4 Port33 OTG_EP4 Port34 OTG_EP5 Port34 OTG_EP5 Port35 Port35 Port36 Port36 Port37 Port37 Port38 Port38 Port39 Port39 Port40 Port40 Port41 Port41 Port42 Port42 Port43 TWI0 Port43 TWI0 Port44 TWI1 Port44 TWI1 Port45 TWI2 Port45 TWI2 Port46 TWI3 Port46 TWI3 Port47 TWI4 Port47 TWI4 Port48 S_TWI0 Port48 S_TWI0

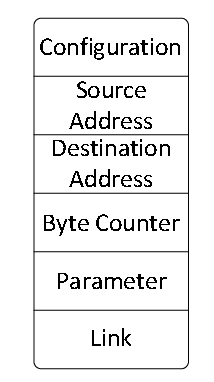

3.9.3.4DMA Descriptor Рисунок 3-19. Дескриптор DMA

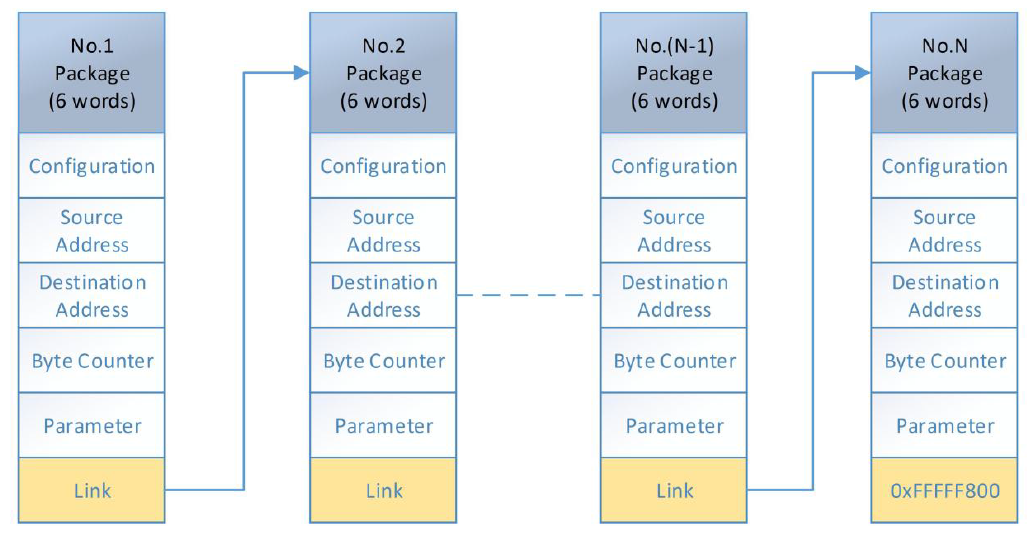

Дескриптор DMA - это информация о конфигурации передачи DMA, которая определяет рабочий режим DMA. Каждый дескриптор включает в себя 6 слов, в свою очередь, конфигурацию, адрес источника, адрес назначения, счетчик байтов, параметр, ссылку. (1) Конфигурация: Настройте следующую информацию с помощью DMA_CFG_REG. Тип DRQ источника и назначения: сигнал DRQ устройств является управляющим сигналом передачи DMA. Режим подсчета переданных адресов: режим ввода-вывода указывает, что адрес фиксируется во время передачи; линейный режим указывает, что адрес увеличивается во время передачи. Длина переданного блока: длина блока - это количество переданных данных DMA в одноразовом допустимом DRQ. Длина блока поддерживает 1-битный, 4-битный, 8-битный или 16-битный режим. Ширина передаваемых данных: ширина данных указывает ширину данных для каждой операции и поддерживает 8-битный, 16-битный, 32-битный или 64-битный режим. (2) Исходный адрес: настройте переданный исходный адрес. (3) Адрес назначения: настройте переданный адрес назначения. (4) Счетчик байтов: настройте количество пакета. Максимальный размер пакета не превышает (2 ^ 25-1) байт. Если количество пакета достигает максимального значения, даже если DRQ действителен, DMA должен остановить текущую передачу. (5) Параметр: Настройте интервал между блоками данных. Параметр действителен для периферийных устройств без памяти. Когда DMA обнаруживает, что DRQ имеет высокий уровень, DMA передает цикл блока. И во время изменение DRQ игнорируется. После передачи DMA ожидает цикла установки (WAIT_CYC), затем выполняет следующее обнаружение DRQ. (6) Ссылка: если значение ссылки 0xFFFFF800, текущий пакет находится в конце связанного списка. DMA прекратит передачу после передачи пакета; если значение ссылки не 0xFFFFF800, значение ссылки считается адресом дескриптора следующего пакета. Рисунок 3-20. Цепная передача DMA

3.9.3.5Прерывание Прерывание от половины пакета разрешено, DMA отправляет прерывание от половины пакета после завершения передачи половины пакета. Общее прерывание пакета включено, DMA отправляет прерывание конца пакета после завершения полной передачи пакета. Общее прерывание очереди разрешено, DMA отправляет прерывание конца очереди после завершения всей очереди. Обратите внимание, что когда ЦП не отвечает на прерывания вовремя или два прерывания DMA генерируются очень близко, последующее прерывание может перекрыть первое. Итак, для ЦП DMA имеет только источник системного прерывания.

3.9.3.6Безопасность DMA поддерживает систему Trustzone и поддерживает безопасный режим канала DMA. Каждый канал DMA по умолчанию защищен. Когда система Trustzone включена, DMA защищен, только защищенные устройства могут получить доступ к DMA. Когда канал DMA настроен как незащищенный, тогда канал может получить доступ только к незащищенной области памяти. DMA не может записывать данные в защищенную область памяти, данные обратного чтения из защищенной области памяти равны 0.

3.9.3.7Синхронизация стробирования Модуль DMA CLK GATE - это модуль синхронизации с автоматическим аппаратным управлением. Модуль DMA CLK GATE в основном используется для генерации часов субмодуля DMA и локальной схемы в модуле, включая синхронизацию канала и синхронизацию общедоступной части. Стробирование канала указывает, что часы DMA могут автоматически открываться, когда система обращается к текущему регистру канала DMA и канал DMA включен. Когда передача DMA завершена, часы канала DMA могут автоматически закрыться после задержки 16 HCLK, при этом часы соответствующего управления каналом и управления FIFO будут закрыты. Тактовый строб общей части указывает, что часы общей цепи могут автоматически закрыться, когда все каналы прямого доступа к памяти открыты. Общая схема включает общую схему модуля управления FIFO, модуля MPORT и часов шины памяти. Стробирование часов DMA может поддерживать все функции, указанные выше, или не программно.

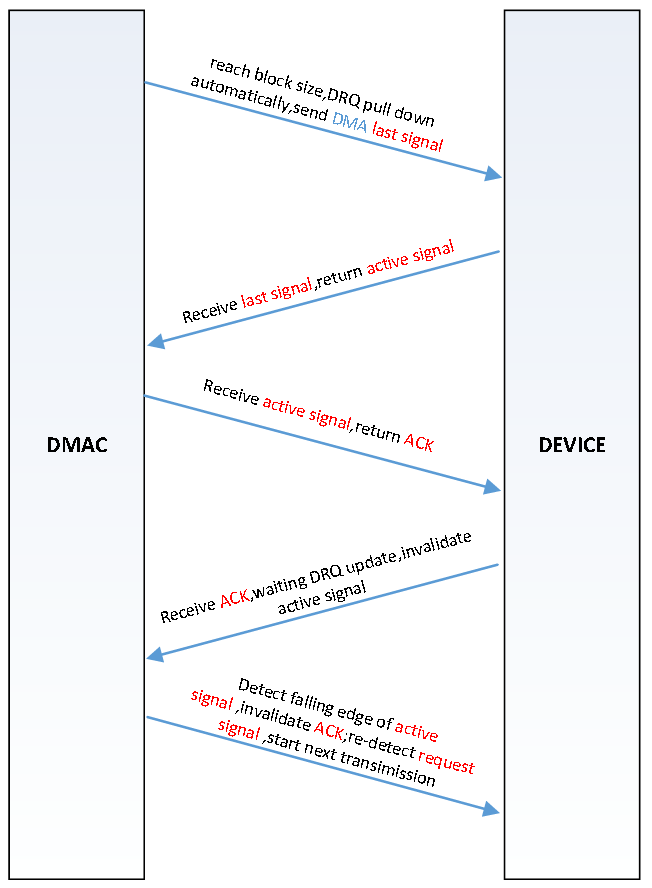

3.9.3.8Режим передачи DMA поддерживает два режима передачи данных: режим ожидания и режим подтверждения. (1) Режим ожидания Когда сигнал запроса устройства поступает в DMA, сигнал запроса устройства преобразуется во внутренний сигнал DRQ через счетчик блока и ожидания. Преобразованный принцип заключается в следующем. Когда DMA обнаруживает, что внешний сигнал запроса действителен, DMA начинает работать с устройством, внутренний DRQ всегда удерживает высокий уровень до того, как достигается рабочий объем блока. Когда объем передачи DMA достигает рабочего объема блока, внутренний DRQ автоматически понижается. После того, как внутренний DRQ автоматически удерживает низкий уровень в цикле DMA времени счетчика ожидания, DMA перезапускается для обнаружения внешнего запроса, если сигнал внешнего запроса действителен, то начинается следующая передача. (2) Режим рукопожатия Когда DMA обнаруживает, что внешний сигнал запроса действителен, DMA начинает работать с устройством, внутренний DRQ всегда удерживает высокий уровень до того, как будет достигнут рабочий объем блока. Когда объем передачи DMA достигает рабочего объема блока, внутренний DRQ автоматически понижается; тем временем в рамках последней операции DMA перед достижением количества блоков DMA следует за операционным запросом для одновременной отправки последнего сигнала DMA. Последний сигнал DMA, который используется как часть запроса DMA, передается на шине, когда устройство получает рабочее требование DMA последним на шине, устройство может определить длину блока передачи DMA, завершенную, то есть перед повторной передачей запроса, DMA операция не может появиться, и на контроллер DMA генерируется активный сигнал DMA. Обратите внимание, что каждый сигнал DRQ устройства соответствует активному сигналу, если устройство имеет много сигналов DRQ, тогда DMA возвращает другой активный сигнал через другую работу шины. Когда DMA получает переданный активный сигнал устройств, сигнал DMA ACK возвращается устройствам. После того, как устройство получает сигнал DMA ACK, если все операции устройств завершены, статус FIFO и статус DRQ обновляются, тогда активный сигнал устанавливается как недействительный. Когда DMA обнаруживает спад активного сигнала, соответствующий сигнал ACK устанавливается как недопустимый, и DMA перезапускается для обнаружения внешнего сигнала запроса. Если сигнал запроса действителен, то начинается следующая передача. Рисунок 3-21. Режим передачи DMA.

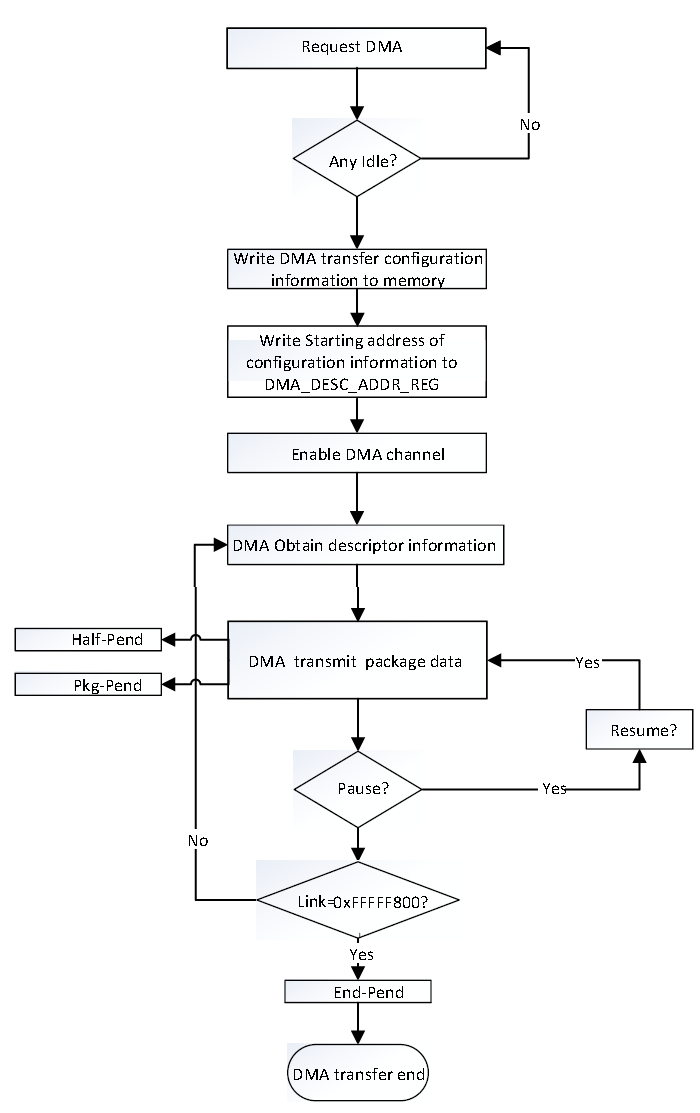

3.9.3.9Функция автоматического выравнивания DMA поддерживает выравнивание адресов устройств без ввода-вывода, то есть, когда начальный адрес устройств без ввода-вывода не выровнен по 32 байтам, DMA сначала выравнивает пакетную передачу в пределах 32 байтов до 32 байтов. Если устройство канала DMA настроено на тип без ввода-вывода и начальный адрес равен 0x86, то DMA сначала выравнивает 26-байтовую пакетную передачу с 0xA0, затем DMA передает 64-байтовым пакетом (максимально допустимый объем передачи MBUS) . Выравнивание адреса по 32 байта помогает повысить эффективность доступа к DRAM. Устройства ввода-вывода не поддерживают выравнивание адресов, поэтому разрядность устройств ввода-вывода должна соответствовать смещению адреса, в противном случае DMA игнорирует несогласованность и косвенно передает данные соответствующей разрядности по адресу. Адрес дескриптора DMA не поддерживает функцию автоматического выравнивания. Адрес должен обеспечивать выравнивание по словам, иначе DMA не сможет идентифицировать дескриптор. 3.9.3.10.1. Управление часами DMA Часы DMA синхронны с часами AHB1. Убедитесь, что перед доступом к регистру DMA откройте бит стробирования DMA часов AHB1. Входной сигнал сброса DMA асинхронен с AHB1 и по умолчанию имеет низкий уровень. Убедитесь, что отменили сигнал сброса DMA перед доступом к регистру DMA. Чтобы избежать неопределенного состояния в регистрах, во-первых, деактивируйте сигнал сброса, во-вторых, откройте бит стробирования AHB1. DMA имеет функцию автостробирования часов, часы DMA можно отключить в состоянии ожидания DMA с помощью программного обеспечения для снижения энергопотребления. DMA по умолчанию включает автостробирование часов. 3.9.3.10.2. Процесс передачи DMA Процесс передачи DMA выглядит следующим образом. (1) Запросите канал DMA и оцените состояние незанятости канала по тому, включен ли канал DMA. (2) Запишите дескриптор (6 слов) в память, дескриптор должен быть выровнен по словам. Подробнее см. 3.9.3.4 Дескриптор DMA. (3) Запишите начальный адрес дескриптора хранения в DMA_DESC_ADDR_REG. (4) Включите канал DMA и запишите соответствующий канал в DMA_EN_REG. (5) DMA получает информацию дескриптора. (6) Начать передачу пакета, когда половина пакета завершена, DMA отправляет прерывание передачи полупакета; когда весь пакет завершен, DMA отправляет прерывание передачи конца пакета. Состояние прерывания может быть прочитано DMA_IRQ_PEND_REG. (7) Установите DMA_PAU_REG, чтобы приостановить или возобновить передачу данных. (8) После завершения полной передачи пакета DMA решает начать следующую передачу пакета или завершить передачу по ссылке дескриптора. Если ссылка 0xFFFFF800, передача завершается; если ссылка имеет другое значение, следующий пакет начинает передачу. Когда передача заканчивается, DMA отправляет прерывание передачи конца очереди. (9) Отключите канал DMA. Рисунок 3-22. Процесс передачи DMA 3.9.3.10.3. DMA прерывание (1) Разрешить прерывание: записать соответствующее разрешение прерывания в DMA_IRQ_EN_REG, когда соответствующее условие прерывания удовлетворяется, генерируется соответствующее прерывание. (2) После входа в процесс прерывания напишите DMA_IRQ_PEND_REG, чтобы очистить отложенное прерывание, и выполните процесс ожидания прерывания. (3) Возобновить прерывание и продолжить выполнение прерванного процесса.

3.9.4. Рекомендации по программированию (1) Ширина передачи устройства типа IO соответствует смещению начального адреса. (2) Протокол MBUS не поддерживает операцию чтения нецелочисленного слова, поэтому для операции чтения нецелочисленного слова устройство должно игнорировать избыточные несогласованные данные между шириной данных и конфигурацией, то есть устройство нецелого слова должно интерпретировать DMA спрос через его ширину FIFO вместо ширины спроса на чтение. (3) Когда передача DMA приостановлена, это эквивалентно недопустимому DRQ. Поскольку команда передачи DMA имеет определенную временную задержку, DMA не остановит передачу немедленно, пока не завершится текущая команда и команда в Arbiter, не более 32-байтовых данных. Пример приложения DMA: Writel (0x00000000, mem_address + 0x00); // Установка конфигурации, mem_address должен быть выровнен по словам Writel (0x00001000, mem_address + 0x04); // Установка начального адреса для исходного устройства Writel (0x20000000, mem_address + 0x08); // Установка начального адреса для устройства назначения Writel (0x00000020, mem_address + 0x0C); // Установка размера пакета данных Writel (0x00000000, mem_address + 0x10); // Установка параметра Writel (0xFFFFF800, mem_address + 0x14); // Установка начального адреса для следующего дескриптора Writel (mem_address, 0x01C02000 + 0x100 + 0x08); // Установка начального адреса для дескриптора DMA channel0 descriptor do { if(mem_address == readl(0x01C02000 + 0x100 + 0x08)); break; } while(1); // Убедитесь, что операция записи верна Writel (0x000000001, 0x01C02000 + 0x100 + 0x00); // Включить передачу DMA по каналу 0 DMA поддерживает увеличивающийся пакет данных при передаче, здесь следует отметить несколько моментов. Когда значение регистра адреса дескриптора канала DMA равно 0xFFFFF800, это означает, что канал DMA получил обратно дескриптор последнего пакета. Когда канал DMA завершил передачу пакетных данных, канал DMA автоматически остановит передачу данных. Если пакеты данных необходимо увеличить, то сначала важно оценить, получил ли канал DMA обратно дескриптор последнего пакета, если канал DMA вернул дескриптор последнего пакета, то это невозможно для увеличения пакет данных, канал DMA нужно запустить заново. Если DMA не передает последний пакет, то адрес последнего дескриптора 0xFFFFF800 может быть изменен на начальный адрес следующего дескриптора. Чтобы убедиться, что данные были изменены, мы можем снова прочитать значение регистра адреса дескриптора канала DMA после изменения данных. Если нет 0xFFFFF800, это означает, что увеличение пакета данных выполнено успешно, в противном случае - сбой. Поскольку для процесса увеличения пакета данных требуется некоторое время, в это время канал DMA может вернуть дескриптор последнего пакета. В настоящий момент мы можем снова прочитать регистр текущего адреса источника канала DMA и регистр текущего адреса назначения канала DMA, если увеличивающийся адрес памяти согласуется с информацией о возрастающем пакете данных, то увеличивающийся пакет данных является успешным, в противном случае - неудачным. Чтобы обеспечить более высокий процент успешных попыток, рекомендуется увеличить пакет данных до прерывания половины пакета предпоследнего пакета данных.

|

|