3.1. Отображение памяти

3.10. Контроллер термодатчика

3.11. Подключение периферийной системы PSI

3.12. Модуль управления памятью ввода-вывода IOMMU

3.13. Часы реального времени RTC

3.2. Конфигурация CPUX

3.3. Контроллер синхрогенератора

3.5. Конфигурация системы

3.6. Таймер

3.8. Универсальный контроллер прерываний

Глава 3. Система - System

Раздел 3.12. Модуль управления памятью ввода-вывода IOMMU - Input/Output Memory management unit (IOMMU)

3.12. IOMMU

3.12.1. Обзор

IOMMU (модуль управления памятью ввода-вывода) разработан для конкретных требований к памяти продукта. Он сопоставляет виртуальный адрес (отправленный памятью периферийного доступа) с физическим адресом. IOMMU позволяет несколькими способами управлять расположением физического адреса, и он может использовать физический адрес, который имеет потенциально конфликтное сопоставление для различных процессов для выделения пространства памяти, а также позволяет применять прерывистое сопоставление адресов в непрерывное виртуальное адресное пространство.

Особенности:

Поддерживает отображение виртуального адреса на физический адрес посредством аппаратной реализации Поддерживает параллельное отображение адресов DE, DI, VE_R, VE, G2D Независимая поддержка функции обхода DE, DI, VE_R, VE, G2D Независимая поддержка предварительной выборки DE, DI, VE_R, VE, G2D Независимая поддержка механизма обработки прерываний DE, DI, VE_R, VE, G2D Поддерживает 2 уровня TLB (TLB уровня 1 для специального использования и TLB уровня 2 для совместного использования) Поддержка TLB полностью очищена и частично отключена Поддерживает запуск PTW при пропуске TLB Поддерживает проверку разрешения3.12.2. Блок-схема

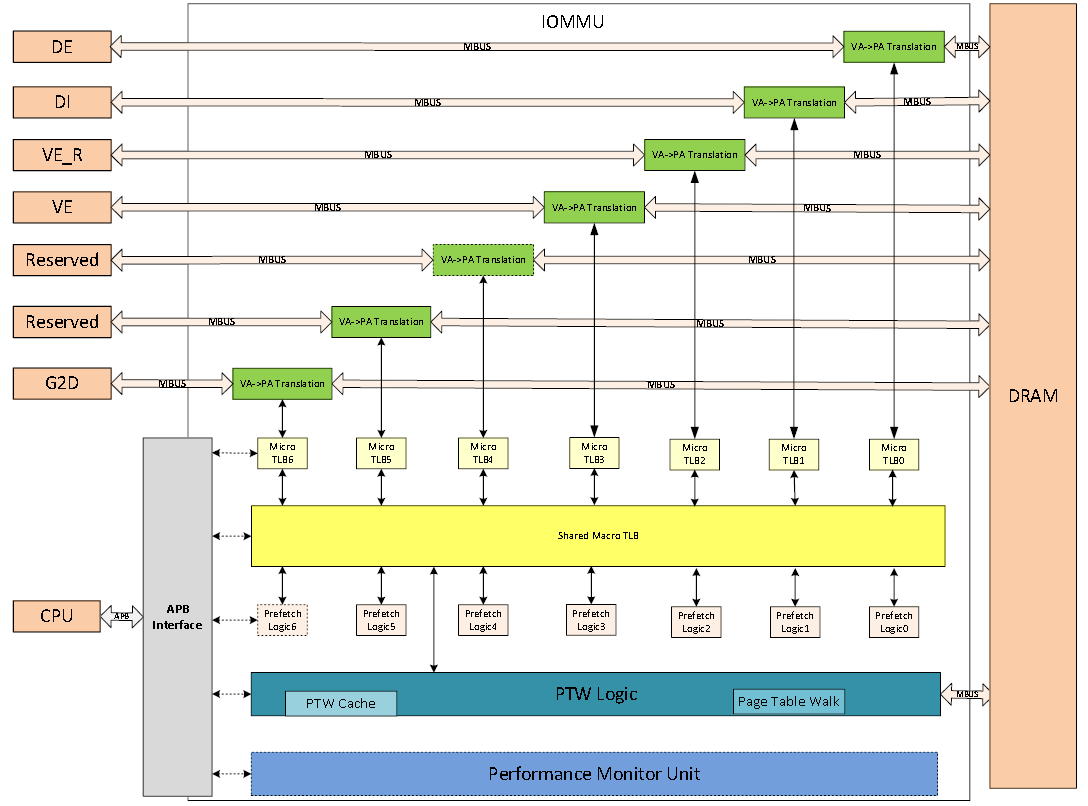

Внутренний модуль IOMMU в основном состоит из следующих частей.На рис. 3-28 показана внутренняя блок-схема IOMMU.

Рисунок 3-28 Внутренняя блок-схема IOMMU.

Таблица 3-8. Соотношение между ведущим устройством (master) и модулем

Номер | Модуль

3.12.3. Операции и функциональные описания

3.12.3.1

Источники синхронизации

IOMMU содержит в модуле два тактовых домена. Отображение адресов создается тактовой областью MBUS, а обработка регистров и прерываний генерируется тактовой областью APB. Эти два домена являются асинхронными, и они из разных источников синхронизации.

3.12.3.2

Режимы работы

1. Инициализация

2. Изменение адреса

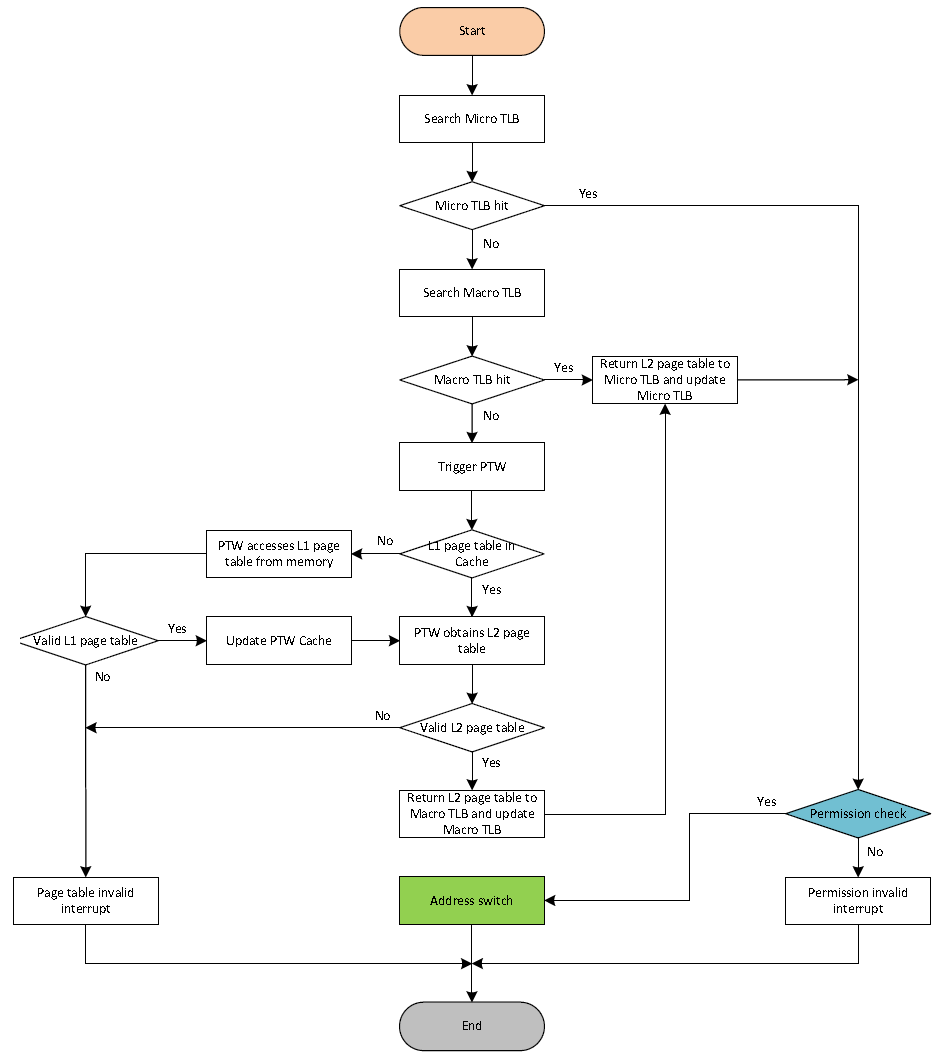

В процессе отображения адреса периферийный виртуальный адрес VA [31:12] извлекается в TLB уровня 1, когда TLB попадает, отображение завершается, или они извлекаются в TLB уровня 2 таким же образом.

После открытия функции обхода периферийных устройств путем установки регистра обхода IOMMU, IOMMU не будет отображать адрес для периферийного устройства, набравшего адрес, и будет выводить виртуальный адрес как физический адрес.

Типичное приложение выглядит следующим образом.

- a) Главное устройство отправляет команду передачи, а также отправляет адрес в соответствующий Micro TLB и выполняет поиск виртуального адреса, соответствующего таблице страниц уровня 2;

- b) При попадании в Micro TLB он вернет соответствующие физические адреса и таблицу разрешений на странице Level2; в). Модуль преобразования адресов преобразует виртуальный адрес в физический и одновременно проверяет разрешения. Если прошел, перевод завершен.

- a) Главное устройство отправляет команду передачи, а также отправляет адрес в соответствующий Micro TLB и выполняет поиск виртуального адреса, соответствующего таблице страниц уровня 2; б). Если Micro TLB не работает, продолжайте поиск Macro TLB;

- b) Если Macro TLB сработает, он вернет таблицу страниц Level2 в Micro TLB;

- c) Micro TLB получает таблицу страниц и помещает ее в Micro TLB (если этот Micro TLB заполнен, есть действия по замене), в то же время отправляет записи таблицы страниц в модуль трансляции адресов;

- d) Модуль преобразования адресов преобразует виртуальный адрес в физический и одновременно проверяет разрешения. Если пройден, перевод завершен.

- a) Главное устройство отправляет команду передачи, а также отправляет адрес в соответствующий Micro TLB и выполняет поиск виртуального адреса, соответствующего таблице страниц уровня 2;

- b) Если Micro TLB не работает, продолжайте поиск Macro TLB;

- c) Если Macro TLB пропущен, он отправит запрос в PTW, чтобы вернуть соответствующую таблицу страниц;

- d) PTW сначала обращается к кэшу PTW, подтверждает, что требуемая таблица страниц уровня 1 существует в кэше PTW, отправляет таблицу страниц в логику PTW;

- e) Логика PTW возвращает соответствующую таблицу страниц уровня 2 из таблицы страниц памяти в соответствии с таблицей страниц уровня 1, проверяет эффективность и отправляет в Macro TLB;

- f) Макрос TLB хранит таблицу страниц уровня 2 (могут произойти действия по замене) и возвращает таблицу страниц уровня 2 в Micro TLB;

- g) Micro TLB получает записи таблицы страниц, помещает в Micro TLB (если этот Micro TLB заполнен, произойдут действия по замене) и отправляет записи таблицы страниц в модуль трансляции адресов;

- h) Модуль преобразования адресов преобразует виртуальный адрес в физический и одновременно проверяет разрешения. Если пройден, перевод завершен.

- a) Главное устройство отправляет команду передачи, а также отправляет адрес в соответствующий Micro TLB и выполняет поиск виртуального адреса, соответствующего таблице страниц уровня 2; б). Если Micro TLB не работает, продолжайте поиск Macro TLB;

- b) Если Macro TLB пропущен, PTW отправит запрос на возврат соответствующей таблицы страниц; г). PTW обращается к кэшу PTW, отсутствует необходимая таблица страниц уровня 1;

- c) PTW обращается к памяти, получает соответствующую таблицу страниц уровня 1 и сохраняет в кэше PTW; (может произойти замена деятельности)

- d) Логика PTW возвращает соответствующую таблицу страниц уровня 2 из таблицы страниц памяти в соответствии с таблицей страниц уровня 1, проверяет эффективность и отправляет в Macro TLB;

- e) Макрос-TLB хранит таблицу страниц уровня 2 (могут произойти действия по замене) и возвращает таблицу страниц уровня 2 в Micro TLB;

- f) Micro TLB получает записи таблицы страниц, помещает в Micro TLB (если этот Micro TLB заполнен, произойдут действия по замене) и отправляет записи таблицы страниц в модуль трансляции адресов;

- g) Модуль преобразования адресов преобразует виртуальный адрес в физический и одновременно проверяет разрешения. Если пройден, перевод завершен.

- a) Проверка разрешений всегда выполняется при преобразовании адресов;

- b) Как только при проверке разрешений возникает ошибка, новый доступ мастера приостанавливается, прежде чем это посещение продолжится;

- c) Установите регистр статуса ошибки;

- d) Триггер прерывания.

- a) Недопустимая таблица страниц уровня 1 проверяется, когда логика PTW считывает таблицу страниц нового уровня из памяти;

- b) PTW последовательно считывает из памяти две записи таблицы страниц (64-битные данные, полную строку кэша) и сохраняет в кэше PTW;

- c) Если текущая таблица страниц обнаружена как недопустимая, тогда устанавливается флаг ошибки и запускается прерывание, строка кэша должна быть признана недействительной.

Примечание

Недопустимая таблица страниц имеет две ситуации: чтение целевой таблицы страниц из памяти недопустимо; и таблица страниц, хранящаяся в кэше PTW с таблицей целевой страницы, оказывается недействительной после использования;

Если таблица страниц недействительна, то общая строка кэша (то есть две таблицы страниц) должна быть признана недействительной.

- а) Недопустимая таблица страниц уровня 2 проверяет, когда TLB макроса считывает таблицу страниц нового уровня из памяти;

- б) TLB макроса последовательно считывает из памяти две записи таблицы страниц (64-битные данные, полную строку кэша) и сохраняет в TLB макроса;

- в) Если текущая таблица страниц обнаружена как недопустимая, тогда устанавливается флаг ошибки и запускается прерывание, строка кэша должна быть признана недействительной.

Примечание

Недопустимая таблица страниц имеет две ситуации: чтение целевой таблицы страниц из памяти недопустимо; и таблица страниц, хранящаяся в Macro TLB с таблицей целевой страницы, оказывается недействительной после использования.

Если таблица страниц недействительна, то общая строка кэша (то есть две таблицы страниц) должна быть признана недействительной.

Процесс переключения внутреннего адреса показан на Рисунке 3-29.

Рисунок 3-29. Процесс внутреннего переключения

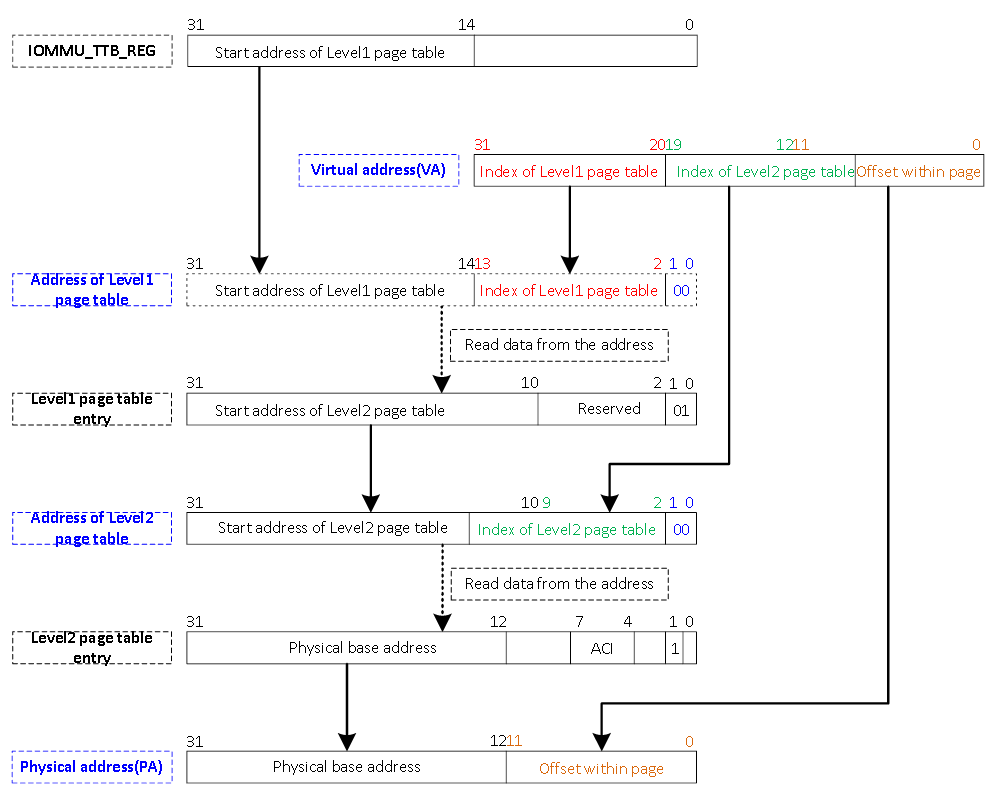

3. Отображение VA-PA

Таблица страниц IOMMU определяется как отображение уровня 2, первый уровень - это отображение адресного пространства 1M, второй уровень - адресное пространство 4K. Эта версия не поддерживает 1 КБ, 16 КБ и другие размеры таблиц страниц. IOMMU поддерживает только таблицу страниц, ее значение:

Рисунок 3-30. Процесс переключения VA-PA

4. Очистить и аннулировать TLB

При обновлении содержимого многостраничной таблицы или изменении адреса таблицы все сопоставления VA-PA, которые были кэшированы в TLB, больше не будут действительны, тогда вам необходимо настроить регистр включения сброса TLB IOMMU, чтобы очистить TLB или PTW Cache. Сначала приостановите доступ к TLB или кэшу, затем настройте соответствующий бит сброса регистра разрешения сброса TLB IOMMU, после того как операция вступит в силу, связанные периферийные устройства могут продолжать отправлять новые операции доступа к памяти.

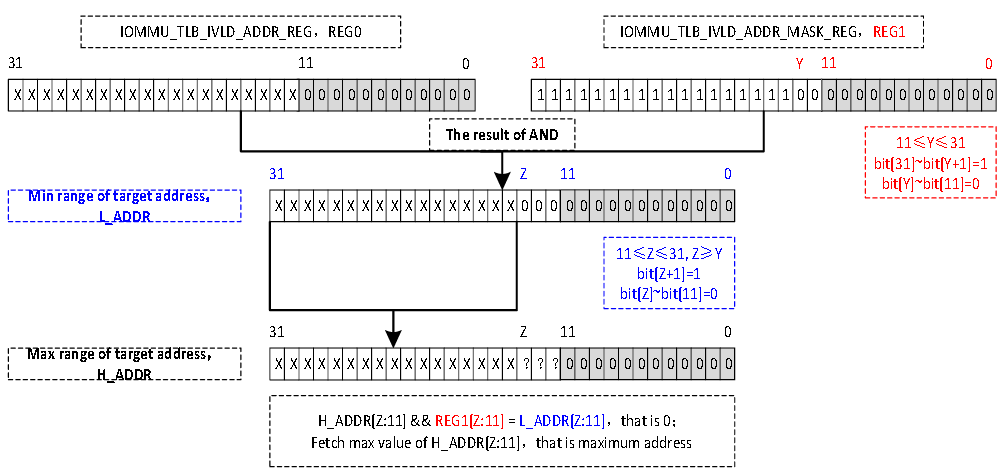

Когда какая-либо таблица страниц является недопустимой или неверным отображением, вы можете установить соответствующий регистр TLB Invalidation, чтобы сделать недействительными пары сопоставления TLB VA-PA. Недопустимый TLB поддерживает два режима.

(1) Режим 0

- Значение регистра маски адреса недействительности TLB IOMMU не может быть меньше регистра адреса недействительности TLB IOMMU.

- Старший бит регистра маски адреса недействительности TLB IOMMU должен быть непрерывным 1, младший бит должен быть непрерывным 0, например, 0xfffff000, 0xffffe000, 0xffffc000, 0xffff8000, 0xffff0000 принадлежит разрешенному значению и 0xffffd000, 0xffffb000, 0xffffa000, 0xffff9000, 0xffff7000 принадлежит к недопустимым значениям.

Наконец, настройте регистр включения недействительности TLB IOMMU, чтобы разрешить недопустимую операцию. Одним из способов определения недопустимого адреса является получение максимального допустимого бита и определение диапазона целевого адреса с помощью целевого адреса И адреса маски. Процесс показан следующим образом.

Рисунок 3-31. Недопустимый диапазон адресов TLB

Например:

- a) Когда значение регистра маски адреса недействительности TLB IOMMU по умолчанию равно 0xFFFFF000, результатом AND является целевой адрес, то есть недействителен только целевой адрес.

- b) Когда значение регистра маски адреса недействительности TLB IOMMU равно 0xFFFF0000, значение регистра адреса недействительности TLB IOMMU равно 0xEEEE1000, тогда диапазон целевых адресов составляет от 0xEEEE0000 до 0xEEEEF000.

- c) Когда значение регистра маски адреса недействительности TLB IOMMU равно 0xFFFFC000, значение регистра адреса недействительности TLB IOMMU равно 0xEEEE8000, тогда диапазон целевых адресов составляет от 0xEEEE8000 до 0xEEEEB000.

- d) Когда значение регистра маски адреса недействительности TLB IOMMU равно 0xFFFF8000, значение регистра адреса недействительности TLB IOMMU равно 0xEEEEC000, тогда диапазон целевых адресов составляет от 0xEEEE8000 до 0xEEEEF000.

- e) Когда значение регистра маски адреса недействительности TLB IOMMU равно 0xFFFFC000, значение регистра адреса недействительности TLB IOMMU равно 0xEEEE0000, тогда диапазон целевых адресов составляет от 0xEEEE0000 до 0xEEEE3000.

(2) Режим 1

3.12.3.3

Формат таблицы страниц

1. Таблица страниц уровня 1

Формат таблицы страниц Уровня 1 следующий.

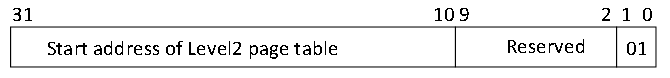

Рисунок 3-32. Формат таблицы страницы уровня 1 Бит [31:10]: базовый адрес таблицы страниц уровня 2; Бит [9: 2]: зарезервирован; Бит [1: 0]: 01 - действительная таблица страниц; другие виноваты;

2. Таблица страниц уровня 2

Формат таблицы страниц Уровня 2 следующий.

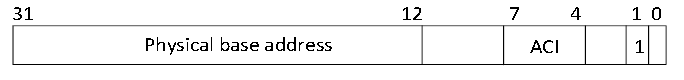

Рисунок 3-33. Формат таблицы страницы уровня 1 Бит [31:12]: физический адрес адреса 4K; Бит [11: 8]: зарезервирован; Бит [7: 4]: ACI, индекс контроля разрешений; соответствуют биту управления разрешениями регистра управления полномочиями домена IOMMU; Бит [3: 2]: зарезервирован; Бит [1]: 1 - действительная таблица страниц; 0 - ошибка; Бит [0]: зарезервирован

3. Индекс разрешений

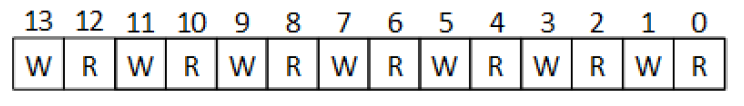

Управление доступом для чтения / записи последовательного регистра, такого как регистр управления полномочиями домена IOMMU, выглядит следующим образом

.

Рисунок 3-34. Контроль разрешений на чтение / запись

Значение регистра управления полномочиями домена IOMMU по умолчанию доступно только для чтения. Другие регистры можно настроить в соответствии с требованиями системы. В процессе переключения адреса соответствующие отношения между ACI и доменом выглядят следующим образом.

Таблица 3-9. Связь между ACI и доменом

ACI | Domain | Register

После включения регистра перезаписи полномочий домена IOMMU разрешение управления чтением / записью может переопределить все регистры управления полномочиями домена IOMMU.

3.12.4. Рекомендации по программированию

3.12.4.1

Сброс IOMMU

Перед операцией сброса программного обеспечения модуля IOMMU убедитесь, что IOMMU никогда не открывается, все операции с шиной завершены, или что DRAM и периферийные устройства уже открывают соответствующий переключатель, чтобы экранировать влияние сброса IOMMU.

3.12.4.2

IOMMU Включить

Перед открытием функции сопоставления адресов IOMMU базовый регистр таблицы трансляции должен быть правильно настроен, или все ведущие устройства находятся в состоянии байпаса, или все ведущие устройства не отправляют команду шины.

3.12.4.3

Настроить TTB

При работе с регистром необходимо закрыть функцию отображения адресов IOMMU, а именно: IOMMU_ENABLE_REG [0] равно 0; или обход функция всех мастеров установлена в 1, или нет состояния команд шины передачи.3.12.4.4

Очистить TTB

В операции сброса весь доступ к TLB / кэшу будет приостановлен; но операция, введенная в TLB, будет продолжена до начала очистки.3.12.4.5

Чтение / запись данных VA

Для виртуального адреса прочтите / запишите соответствующие данные физического адреса, чтобы убедиться, что функция сопоставления адресов модуля IOMMU работает нормально. Сначала убедитесь, что вы выполняете чтение или запись, а затем настройте целевой виртуальный адрес или запись данных, затем начните чтение или запись, после завершения операции проверьте, соответствуют ли результаты ожидаемым.3.12.4.6

Статистика PMU

Когда функция PMU используется в первый раз, установите регистр включения IOMMU PMU, чтобы включить функцию статистики; при чтении соответствующего регистра сбросьте бит разрешения регистра включения IOMMU PMU; когда функция PMU используется в следующий раз, устанавливается первый регистр очистки IOMMU PMU, после сброса счетчика устанавливается бит разрешения регистра включения IOMMU PMU.

Учитывая, что таблица страниц уровня 2 администрирует непрерывный адрес размером 4 КБ, если Micro TLB пропускает непрерывный виртуальный адрес, может потребоваться возврат таблицы страниц уровня 2 для попадания из TLB макроса; но номер попадания не записывается в регистр попаданий Macro TLB и Micro TLB.

Таким образом, истинный расчет показателя попаданий выглядит следующим образом:

Hit Rate = N1 / M1 + (1-N1 / M1) * N2 / M2