3.1. Отображение памяти

3.10. Контроллер термодатчика

3.11. Подключение периферийной системы PSI

3.12. Модуль управления памятью ввода-вывода IOMMU

3.13. Часы реального времени RTC

3.2. Конфигурация CPUX

3.3. Контроллер синхрогенератора

3.5. Конфигурация системы

3.6. Таймер

3.8. Универсальный контроллер прерываний

Глава 3. Система - System

Раздел 3.3. Контроллер синхрогенератора - CCU Controller

3.3. CCU

3.3.1. Обзор

Блок контроллера часов (CCU) управляет конфигурацией PLL и большей частью генерации, разделения, распределения, синхронизации и стробирования тактовых импульсов. CCU входные сигналы включают в себя внешние синхронизирующие импульсы для опорной частоты (24 МГц). Выходы CCU в основном являются тактовыми сигналами для других блоков системы.

CCU включает в себя следующие функции:3.3.2. Операции и функциональные описания

3.3.2.1

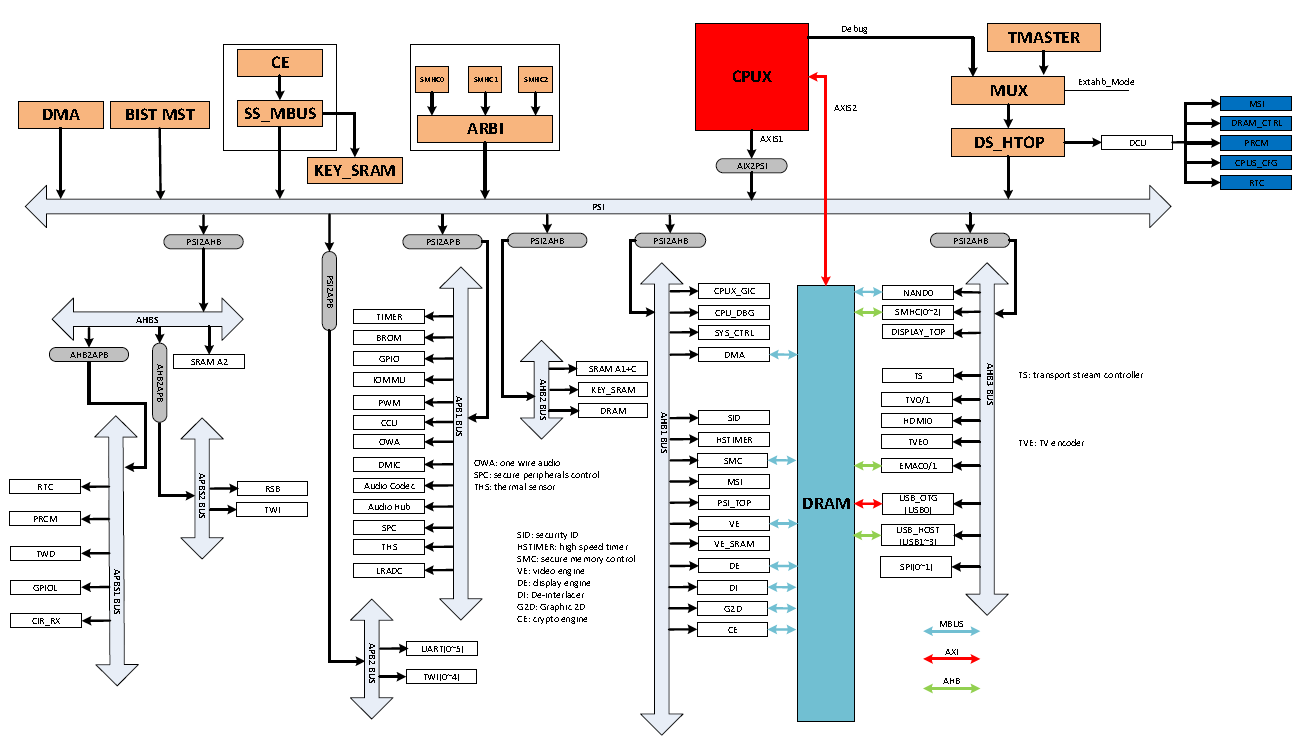

Дерево системной шины

На рис. 3-2 показана блок-схема дерева системной шины.

Рисунок 3-2. Дерево системной шины

3.3.2.2

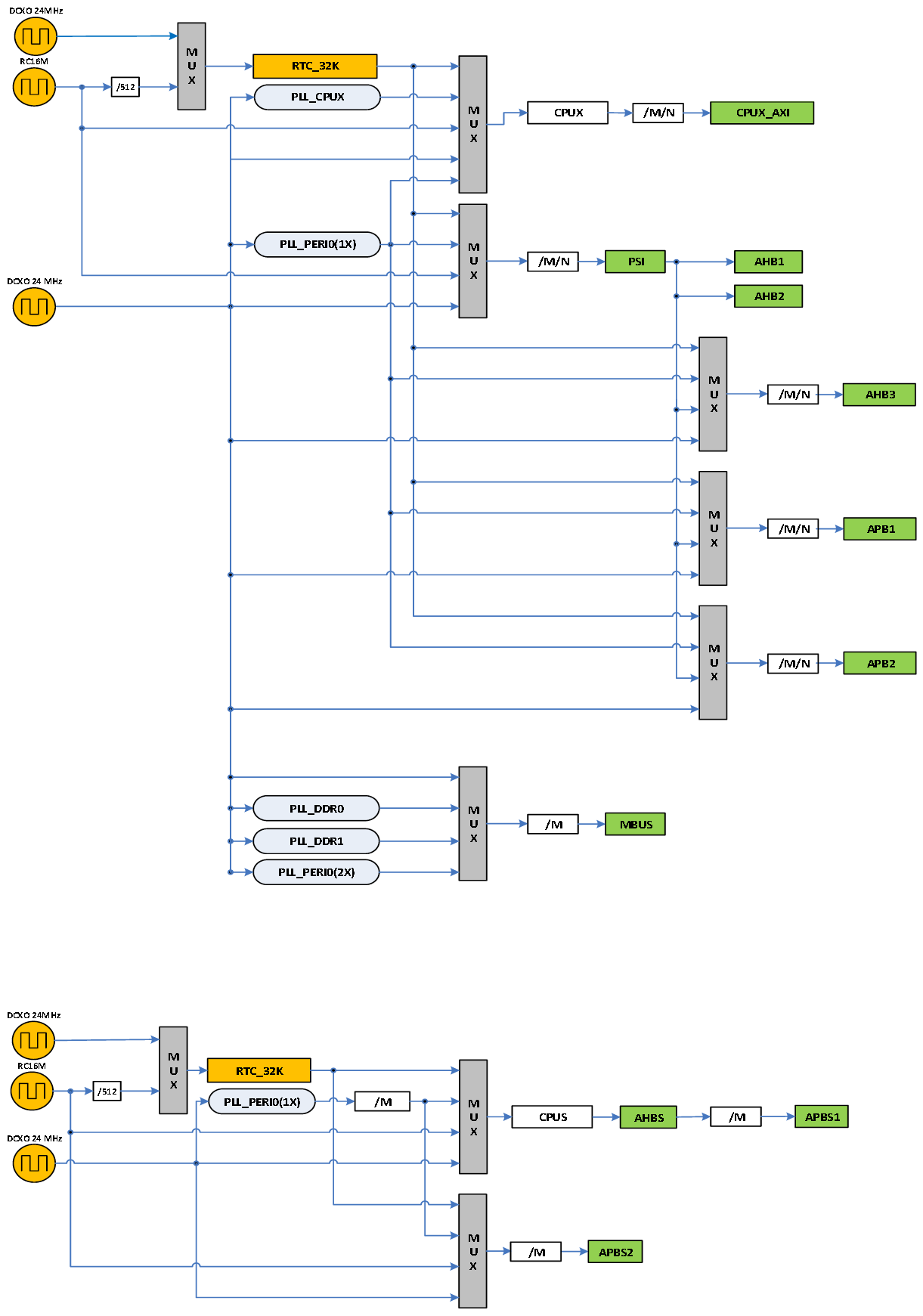

Генерация тактовой частоты шины

Рис. 3-3 описывает генерацию тактовой частоты шины.

Рисунок 3-3. Генерация тактовой частоты шины

3.3.2.3

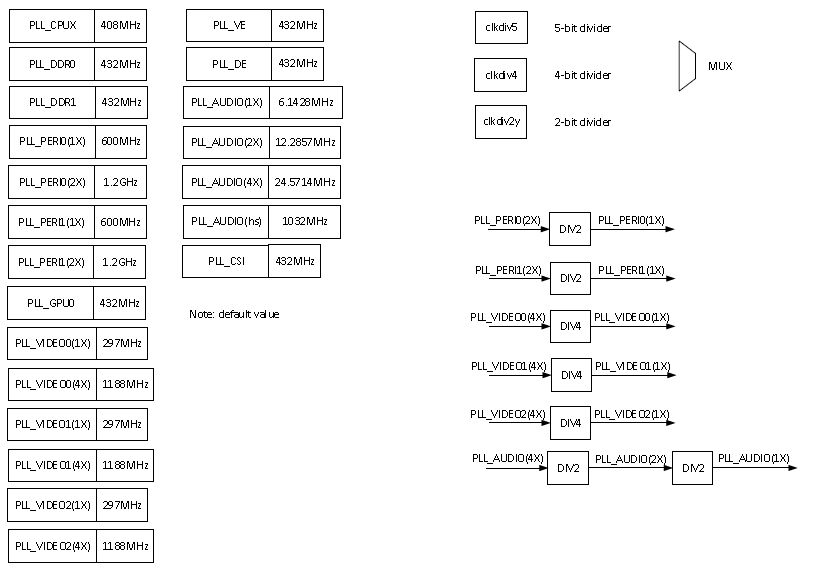

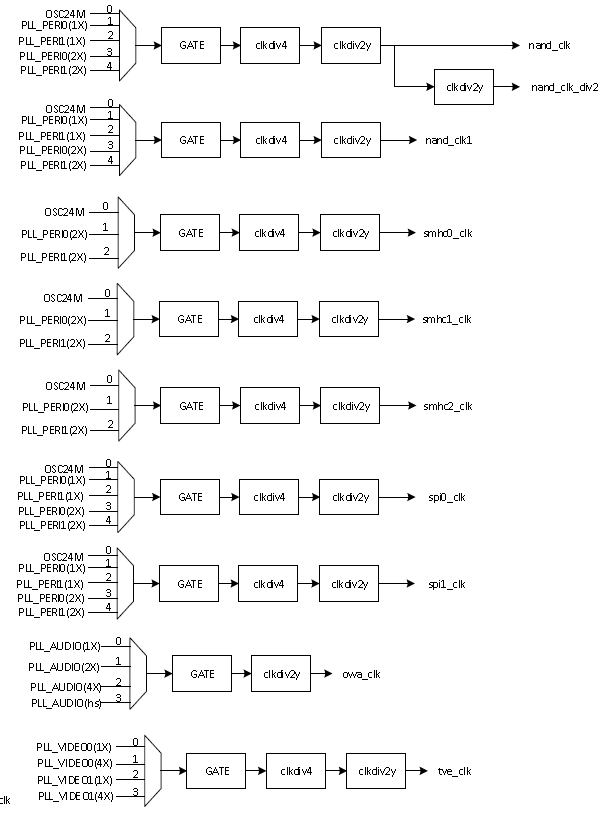

Генерация тактовой частоты модуля

Рис. 3-4 описывает генерацию часов модуля. В скобках указаны типичные частоты по умолчанию.

Рисунок 3-401.

Рисунок 3-402.

Рисунок 3-403.

Рис. 3-4. Генерация тактовой частоты модуля

3.3.2.4

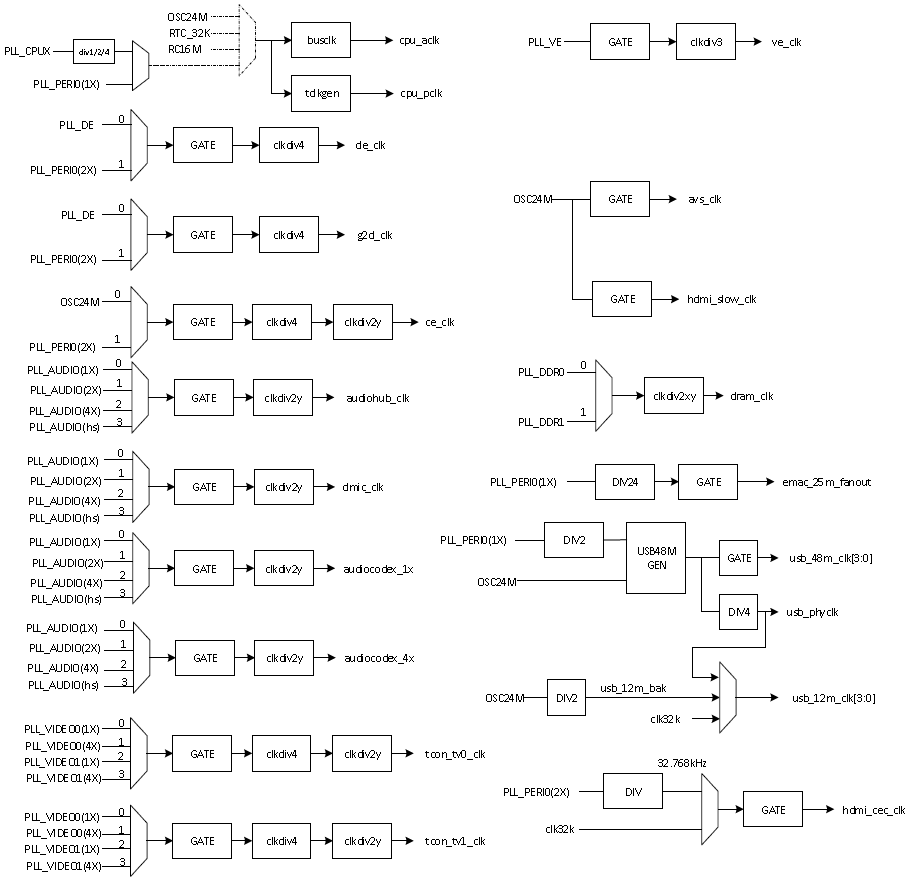

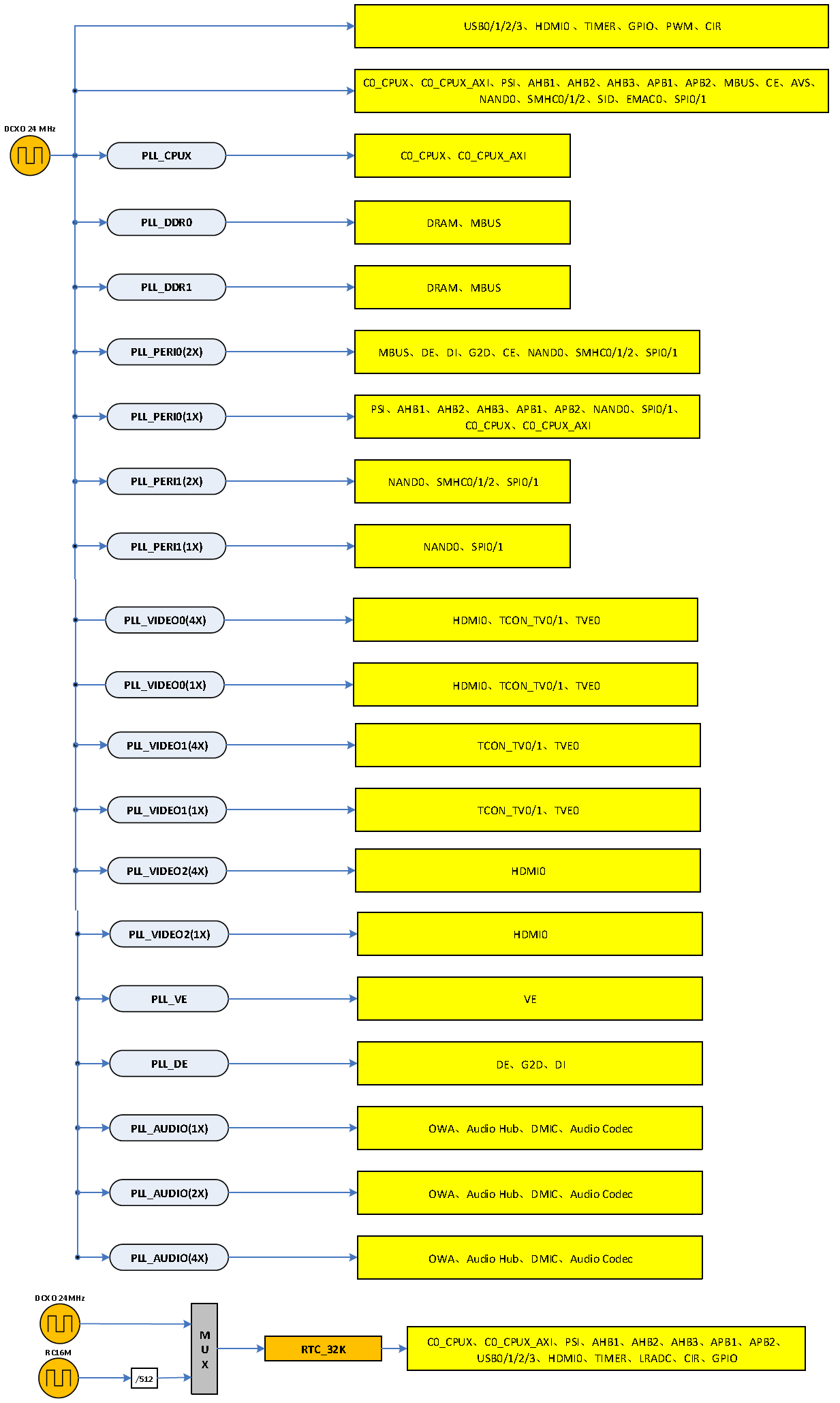

Распределение PLL

На рисунке 3-5 показана блок-схема распределения ФАПЧ.

Рисунок 3-5. Дерево синхронизации модуля

3.3.3. Рекомендации по программированию

3.3.3.1

Регулировка частоты PLL_CPUX

Формула конфигурации частоты PLL_CPUX: PLL_CPUX = 24 МГц * N / P, где параметр N - коэффициент удвоения частоты ФАПЧ, следующая конфигурация параметра может продолжаться после повторной синхронизации ФАПЧ;

- Параметр P представляет собой цифровое пост-частотное деление, которое можно динамически переключать в реальном времени, и он не влияет на нормальную работу системы ФАПЧ.

ЦП PLL поддерживает динамическую настройку частоты (измените значение N). ЦП должен сначала переключиться на более низкую промежуточную частоту, а затем настроить целевую частоту при переключении частоты. Процесс выглядит следующим образом.

3.3.3.2

Регулировка частоты PLL_AUDIO

Формула конфигурации частоты PLL_AUDIO: PLL_AUDIO = 24 МГц * N / M0 / M1 / P. Изменение любого параметра N, M0, M1 и P повлияет на нормальную работу системы ФАПЧ, которую необходимо повторно синхронизировать. Поэтому динамическая настройка не поддерживается.

Для PLL_AUDIO обычно требуются две точки частоты: 24,576 МГц и 22,5792 МГц. Обычно существуют определенные рекомендуемые факторы конфигурации для двух частот. Чтобы реализовать желаемую частотную точку PLL_AUDIO, вам необходимо использовать функцию десятичного деления частоты. Процесс выглядит следующим образом.

Примечание

Коэффициент P PLL_AUDIO - нечетное число, тактовый выходной сигнал не имеет одинаковой нагрузки.

3.3.3.3

Регулировка частоты PLL_DDR

Для тактовой частоты DDR переключатель источника тактовой частоты и коэффициента деления частоты без заусенцев, но регулировка частоты модуля должна осуществляться по следующим правилам.

Контроллер имеет 2 PLL_DDR, процесс настройки следующий.

3.3.3.4

Регулировка частоты общей системы ФАПЧ

3.3.3.5

Отключение ФАПЧ для включения ФАПЧ

3.3.3.6

PLL Enable to PLL Disable

ВНИМАНИЕ

При нормальном использовании ФАПЧ не рекомендуется часто переключать ФАПЧ, потому что переключение ФАПЧ вызовет взаимные помехи между ФАПЧ, что повлияет на стабильность системы. Поэтому рекомендуется отключать ФАПЧ, задав для бита PLL_OUTPUT_EN PLL_CTRL значение 0, вместо того, чтобы записывать 0 в бит разрешения.

3.3.3.7

Конфигурация шины

Часы шины поддерживают динамическое переключение, но процесс переключения должен соответствовать следующим двум правилам.3.3.3.8

Конфигурация модуля синхронизации

Для регистра стробирования шины и сброса модулей сначала отменяется сброс, а затем включается стробирование CLK, чтобы гарантировать отсутствие проблем из-за того, что модуль не сбрасывается синхронно с освобождением.

Для тактовых импульсов модуля, за исключением тактовых импульсов DDR, другие тактовые частоты сначала настраивают источник тактового сигнала и коэффициент деления частоты, а затем освобождают стробирование тактового сигнала (то есть устанавливают его на 1). Для порядка конфигурации источника синхронизации и коэффициента деления частоты выполните следующие правила:

3.3.3.9

Функция распространения спектра

Конфигурация расширенного спектра выполняется следующим образом.Шаг 1. Настройте регистр PLL_CTRL

Примечание

Имея разные формулы расчета ФАПЧ для разных ФАПЧ, обратитесь к каждому регистру PLL_CTRL.Шаг 2: Настройте регистр PLL_PAT

WAVE_BOT = 217 * X1

WAVE_STEP = 217 * (X2-X1) / (24 MHz/PREQ) * 2).