Основные электронные компоненты

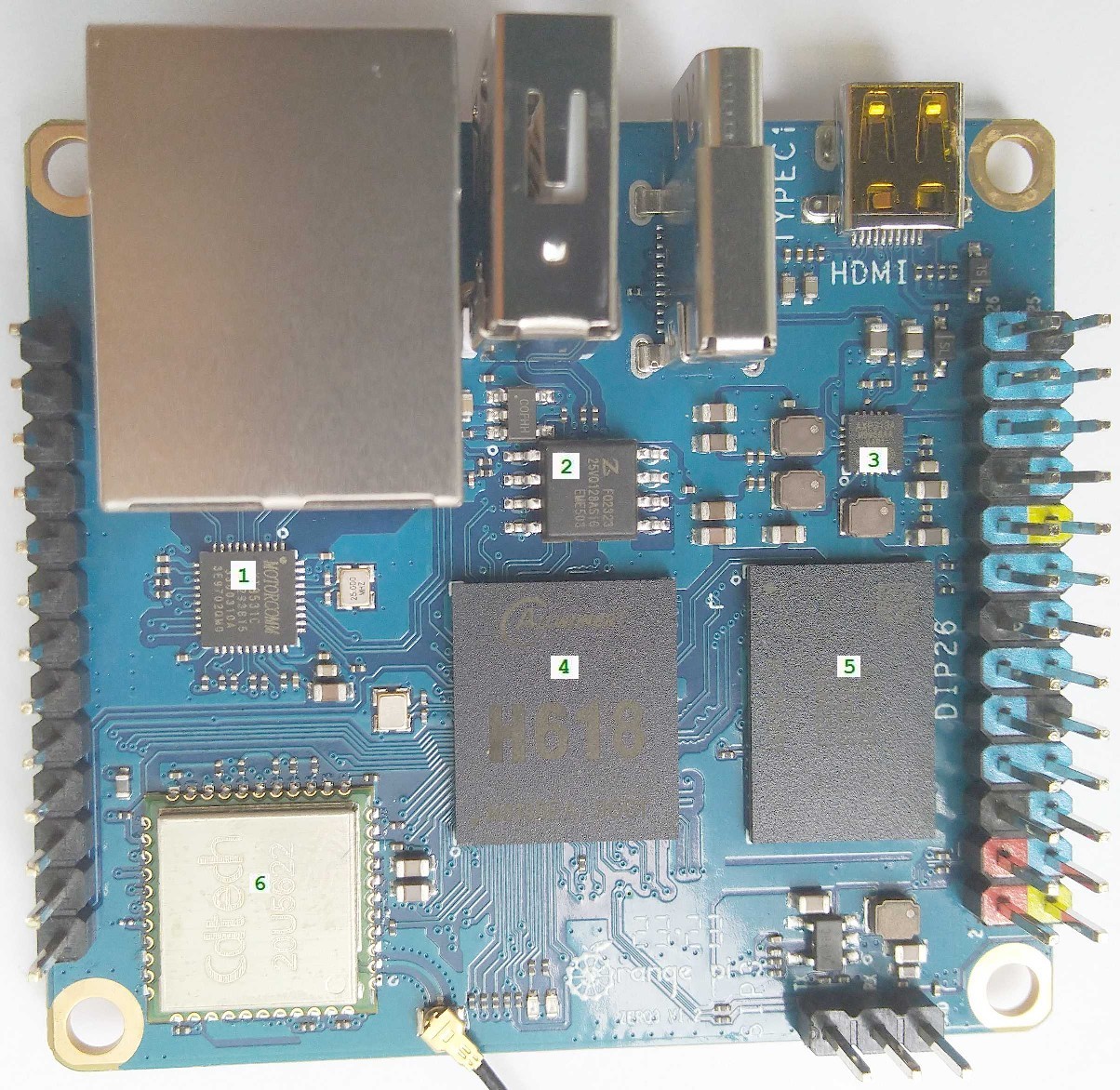

На показанном ниже фото платы установленные на ней микросхемы пронумерованы:

1. Интерфейс Ethernet (1000M Ethernet PHY)

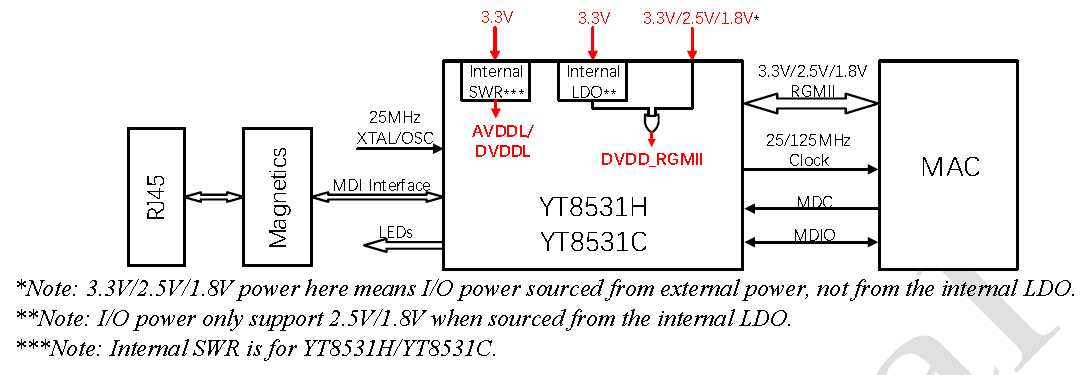

На плате установлена микросхема YI8531C производства Motorcomm (Suzhou Motorcomm Co., Ltd.),

YT8531H / YT8531C / YT8531DH / YT8531DC / YT8531P — это трансивер Ethernet с высокой степенью интеграции, соответствующий стандартам 10BASE-Te, 100BASE-TX и 1000BASE-T IEEE 802.3. Он обеспечивает все необходимые функции физического уровня для передачи и приема пакетов Ethernet по кабелю CAT.5E UTP.

YT8531(D)(P) использует современную технологию DSP и аналоговый интерфейс (AFE) для обеспечения высокоскоростной передачи и приема данных по кабелю UTP. В YT8531(D)(P) реализованы такие функции, как обнаружение кроссовера и автокоррекция, коррекция полярности, адаптивное выравнивание, подавление перекрестных помех, эхоподавление, восстановление синхронизации и коррекция ошибок для обеспечения надежных возможностей передачи и приема на скорости 10 Мбит/с. , 100 Мбит/с или 1000 Мбит/с.

Передача данных между MAC и PHY осуществляется через уменьшенный гигабитный независимый от среды интерфейс (RGMII) для 1000BASE-T, 100BASE-TX и 10BASE-Te. YT8531(D)(P) поддерживает различные сигнальные напряжения RGMII, включая 3,3 В, 2,5 В и 1,8 В.

YT8531(D)(P) оснащен собственной функцией Motorcomm под названием LRE100-4, которая позволяет устройству автоматически согласовывать и подключаться к партнерам по связи, совместимым с LRE100-4, в приложениях с увеличенным радиусом действия кабеля до 400 метров при скорости 100 Мбит/с через кабель CAT 5Е.

Ссылка на спецификацию: YI8531 Datasheet

Оригинал принципиальной схемы: Схема OpiZero3 - л.6

2. Микросхема SPI NOR - Flash память с последовательным интерфейсом

На плате установлена одна микросхема с маркировкой 25VQ128ASIG, это SPI NOR память производства компании Zbit Semiconductor емкостью 16 Мбайт (128 Мбит).

Устройство энергонезависимой флэш-памяти ZB25VQ128 поддерживает стандартный последовательный периферийный интерфейс (SPI). Поддерживаются традиционный однобитовый последовательный ввод и вывод SPI (Single I/O или SIO), а также дополнительные двухбитные (Dual I/O или DIO) и четырехбитные (quad I/O или QIO) последовательные протоколы. Этот интерфейс с множественной шириной называется SPI Multi-I/O или MIO.

ZB25VQ128 поддерживает стандартный последовательный периферийный интерфейс (SPI), Dual/Quad I/O SPI, а также 2-тактовый командный цикл Quad Peripheral Interface (QPI):

- Serial Clock

- Chip Select

- Serial Data I/O0 (DI)

- I/O1 (DO)

- I/O2 (WP#)

- I/O3 (HOLD# / RESET#)

Поддерживаются тактовые частоты SPI до 104 МГц, что обеспечивает эквивалентную тактовую частоту 208 МГц (104 МГц x 2) для двойного ввода-вывода и 416 МГц (104 МГц x 4) для четырех вводов/выводов при использовании двойного / четырехкратного ввода/вывода инструкциq Fast Read и QPI

Эти скорости передачи могут превзойти стандартную асинхронную 8- и 16-битную параллельную флэш-память. Режим непрерывного чтения обеспечивает эффективный доступ к памяти всего за 8 тактов инструкций для чтения 24-битного адреса, что позволяет выполнять настоящую операцию XIP (выполнение на месте).

Вывод удержания, вывод защиты от записи и программируемая защита от записи с верхним или нижним управлением массивом обеспечивают дополнительную гибкость управления. Кроме того, устройство поддерживает стандартный идентификатор производителя и устройства JEDEC, а также регистр SFDP, 64-битный уникальный серийный номер и три 256-байтовых регистра безопасности.

ZB25VQ128 представляет собой решение для хранения данных для систем с ограниченным пространством, сигнальными соединениями и мощностью. Гибкость и производительность этих запоминающих устройств лучше, чем у обычных последовательных флэш-устройств. Они подходят для теневого копирования кода в ОЗУ, прямого выполнения кода (XIP) и хранения перепрограммируемых данных.

Ссылка на спецификацию: ZB25VQ128 Datasheet

Оригинал принципиальной схемы: Схема OpiZero3 - л.1

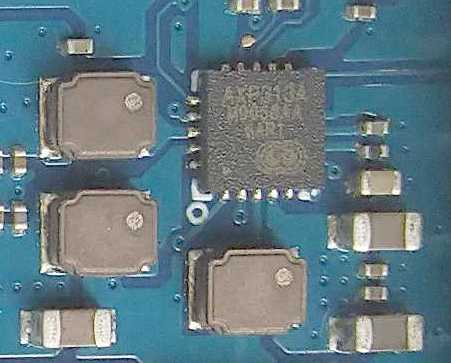

3. Контроллер питания (PMU или PMIC)

На плате установлена микросхема с обозначением AXP313 - это PMU (PMIC) производства компании Синьжихуэй (Shenzhen Xinzhihui Technology Co., Ltd).

Заметим, что в дереве устройств PMU обозначен как AXP1530 (от X-Powers). Однако информации о такой микросхеме найти не удается. В то же время в даташите на AXP313 указано авторство компании X-Powers. Но в списке PMU, производимых X-Powers, нет ни AXP313, ни AXP1530. Однако AXP313 указана в списке PMU, выпускаемых компанией Allwinner (Микросхемы PMU компании Allwinner). Видимо, эта разработка X-Powers была передана в Allwinner (её дочернюю компанию), где и получила новое обозначение.

Ссылка на спецификацию: AXP313 Datasheet (это неофициальный перевод с китайского в виде doc-файла)

Оригинал принципиальной схемы: Схема OpiZero3 - л.4

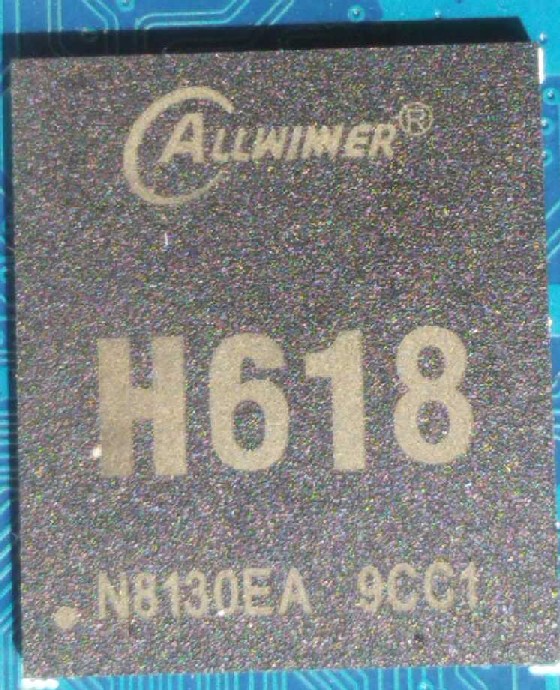

4. Микросхема SoC Allwinner H618

Руководство пользователя (перевод на русский) аналогичного SoC: Руководство пользователя Allwinner H616

Оригиналы принципиальной схемы: Схема OpiZero3 - л.1 Схема OpiZero3 - л.2

5. Микросхема RAM (ОЗУ)

На платах версии RAM 2 Gb установлена микросхема с маркировкой K4F6E3S 4HMGGCJ, это DRAM-память Samsung LPDDR4 SDRAM

Один корпус имеет плотность 16 Gbite (бит), т.е. общая емкость 2 GByte (байт) и организацию x32, т.е. 32-разрядную шину адреса. Микросхема имеет конфигурацию: 64Mb x 16DQ x 8 banks x 2 channels и функционально состоит из двух каналов по 8 Gb 16-ти разрядных слов.

Расшифровка обозначения:

- K4 - Samsung Mobile DRAM Memory

- F - LPDDR4 SDRAM

- 6E - Density 16G, Refresh 8K/32ms

- 3S - Organization x32 (Mono LPDDR4)

- 4 - 8 Bank

- H - Interface:LVSTL_11 VDD1=1.8V, VDD2=1.1V, VDDQ=1.1V

- M - Generation = 1

- M - Package: 200-FBGA (10x15)

- G - Temp, Power: -25 C ~ 85 C (Standard)

- CJ - Speed: 0.536ns@RL32,tRCD18ns, tRP18ns

Ссылка на спецификацию: K4F6E3S Datasheet

Оригинал принципиальной схемы: Схема OpiZero3 - л.3

6. Приемо-передатчик WiFi + BluethoseНа плате установлена микросхема с обозначением CdTech 20U5622 - это гибридная микросхема, которая на принципиальной схеме обозначена как AW859A, обе эти микросхемы являются аналогами AP6256 (ссылка на спецификацию: AP6256 Datasheet)

Микросхема AW859A - производства компании Allwinner(в обозначении микросхемы AW - это Allwinner).

Микросхема 20U5622 - производства компании CdTech (China Dragon Technology Limited).

20U5622 — это объединенный в одном корпусе приемо-передатчик для беспроводной локальной сети (WLAN) и Bluetooth (BT), с поддержкой стандарта IEEE 802.11a/b/g/n/ac WLAN и BT 5.0, который обеспечивает бесшовную интеграцию WLAN/BT и имеет низкое энергопотребление.

Полное наименование: CDW-20U5622-00

Особенности: - Поддерживает маломощный интерфейс SDIO 3.0 для WLAN и интерфейс UART/PCM для BT.

- Обеспечивает высокоинтегрированную систему WLAN на кристалле (SoC) для приложений WLAN 802.11ac 5 ГГц или 802.11n 2,4 ГГц/5 ГГц.

- Поддержка каналов WLAN 2,4 ГГц и 5 ГГц

- Поддержка BT 5.0, BLE и ANT+, а также обратная совместимость с BT 1.x и BT 2.x + Enhanced Data Rate

- Поддерживает несимметричный РЧ-порт для более чистой и дешевой конструкции

- Поддерживает 20 МГц/40 МГц на частоте 2,4 ГГц и поддерживает 20 МГц, 40 МГц или 80 МГц на частоте 5 ГГц.

- Поддерживает многопользовательский MIMO

Ссылка на на спецификацию: CDW20U5622 Datasheet

Оригинал принципиальной схемы: Схема OpiZero3 - л.7