|

Глава 9. Интерфейсы - Interfaces

Раздел 9.1. Двухпроводной интерфейс - Two Wire Interface (TWI)

9.1. TWI

9.1.1. Обзор TWI разработан как интерфейс между центральным процессором и последовательной шиной TWI. Он может поддерживать всю стандартную передачу TWI, включая ведомую и ведущую. Обмен данными по 2-проводной шине осуществляется в побайтовом режиме на основе прерывания или установления связи по запросу. TWI может работать в стандартном режиме (100 кбит / с) или в быстром режиме (400 кбит / с). Для этого указанного приложения поддерживается 10-битный режим адресации. Общая адресация вызовов также поддерживается в ведомом режиме. TWI имеет следующие особенности: Программируется для ведомого или ведущего Поддерживает повторяющийся сигнал СТАРТ Обеспечивает 10-битную адресацию по шине TWI Выполняет арбитраж и синхронизацию часов Собственный адрес и определение общего адреса вызова Прерывание при обнаружении адреса Поддерживает скорость до 400 кбит / с («быстрый режим») Позволяет работать в широком диапазоне входной тактовой частоты Драйвер TWI поддерживает пакетную передачу и DMA, когда TWI работает в ведущем режиме

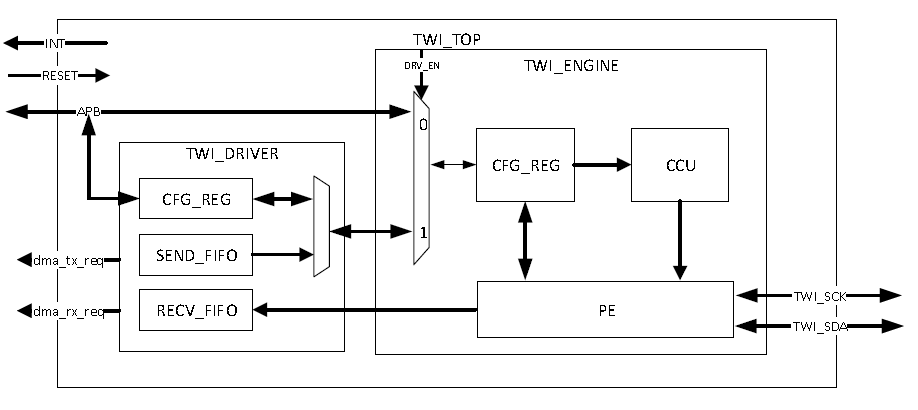

9.1.2. Блок-схема На рисунке 9-1 показана блок-схема TWI. Рисунок 9-1. Блок-схема TWI.

RESET: сигнал сброса модуля INT: сигнал прерывания выхода модуля CFG_REG: регистр конфигурации модуля в TWI PE: кодирование / декодирование пакетов CCU: Модуль тактового контроллера

9.1.3. Операции и функциональные описания

9.1.3.1Внешние сигналы Контроллер TWI имеет 6 TWI. Таблица 9-1 описывает внешние сигналы TWI. TWI_SCK и TWI_SDA - это двунаправленный ввод / вывод, когда TWI настроен как ведущее устройство, TWI-SCK является выходным контактом; когда TWI настраивается как ведомое устройство, TWI-SCK является входным контактом. Неиспользуемые порты TWI используются как порты ввода-вывода общего назначения. Для получения информации о портах ввода-вывода общего назначения см. Контроллер порта в главе 9. Таблица 9-1. Внешние сигналы TWI Сигнал Описание Тип TWI0_SCK TWI0 Вход / выход тактового сигнала, OD TWI0_SDA TWI0 Последовательный ввод / вывод данных, OD TWI1_SCK TWI1 вход / выход тактового сигнала, OD TWI1_SDA TWI1 Последовательный ввод / вывод данных, OD TWI2_SCK TWI2 Вход / выход тактового сигнала, OD TWI2_SDA TWI2 Последовательный ввод / вывод данных, OD TWI3_SCK TWI3 Вход / выход тактового сигнала, OD TWI3_SDA TWI3 Последовательный ввод / вывод данных, OD TWI4_SCK TWI4 Вход / выход тактового сигнала, OD TWI4_SDA TWI4 Последовательный ввод / вывод данных, OD S_TWI0_SCK S_TWI0 Вход / выход тактового сигнала, OD S_TWI0_SDA S_TWI0 Последовательный ввод / вывод данных, OD

9.1.3.2Источники синхроимпульсов Каждый контроллер TWI имеет фиксированный источник тактовой частоты. В Таблице 9-2 описан источник синхронизации для TWI. Пользователи могут видеть Блок контроллера часов (CCU) в главе 3 и Управление сбросом часов (PRCM) для установки часов, конфигурации и информации о стробировании. Таблица 9-2. Источники синхронизации TWI Источники синхро Описание APB2_CLK Источник синхронизации TWI0 / 1/2/3/4, подробности о APB2 см. В CCU APBS2_CLK S_TWI0 тактовый источник, подробности по APBS см. В PRCM После выбора правильных часов для использования TWI0 / 1/2/3/4 пользователь должен открыть ворота TWI и сбросить бит сброса. Для использования S_TWI0 пользователю также необходимо открыть стробирование R-TWI и отпустить бит сброса. Дополнительные сведения о регистре стробирования / сброса см. В спецификации CCU и PRCM.

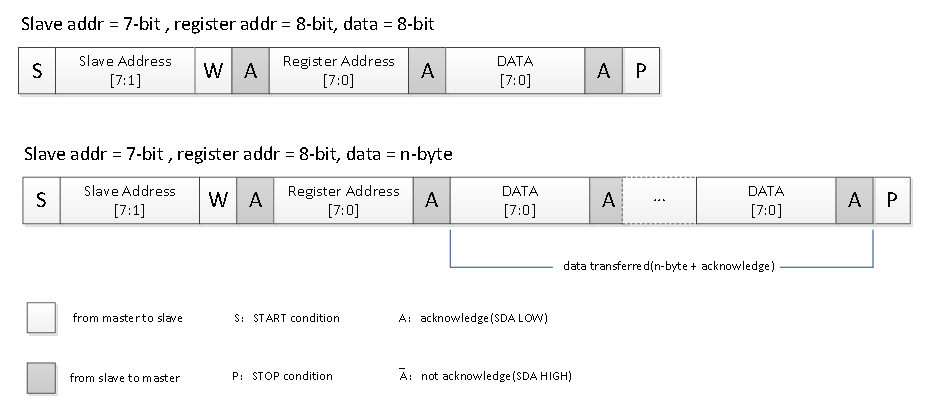

9.1.3.3Время записи / чтения в стандартном и расширенном адресном режиме На рисунке 9-2 показано время записи в 7-битном стандартном адресном режиме. Рисунок 9-2. 7-битное стандартное время записи адреса.

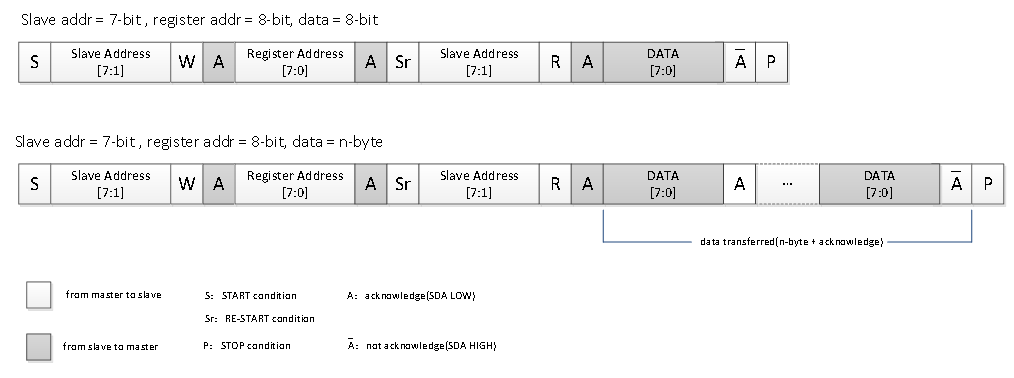

На рисунке 9-3 показано время чтения в 7-битном стандартном адресном режиме. Рисунок 9-3. 7-битное стандартное время чтения адреса

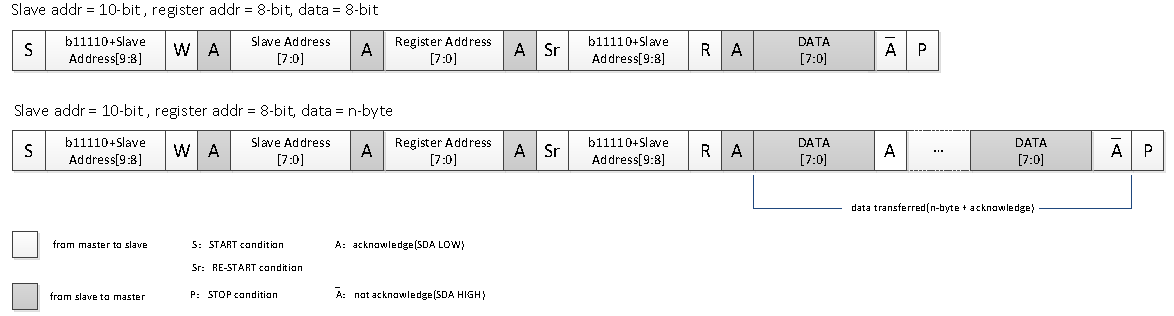

На рисунке 9-4 показано время записи в 10-битном расширенном адресном режиме. Рисунок 9-4. Время записи 10-битного расширенного адреса.

На рисунке 9-5 показано время чтения в 10-битном расширенном адресном режиме. Рисунок 9-5. Время чтения 10-битного расширенного адреса.

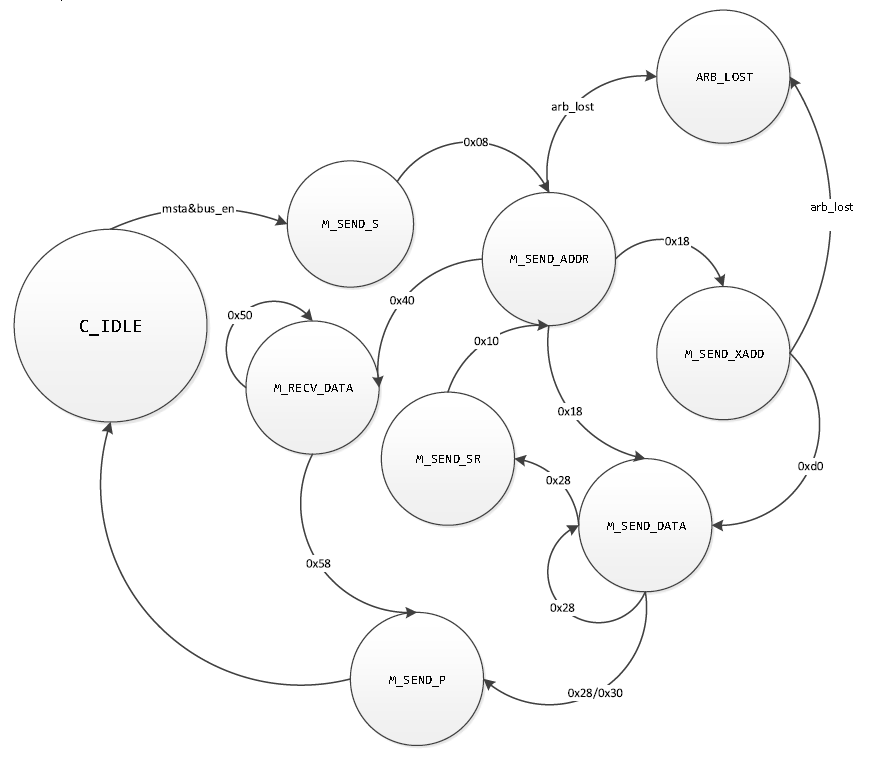

9.1.3.4Диаграмма состояний программирования На рисунке 9-6 показана диаграмма состояний программирования TWI. Для значения между двумя состояниями см. Регистр TWI_STAT в разделе 9.1.6.5. M_SEND_S: мастер отправляет сигнал СТАРТ; M_SEND_ADDR: мастер отправляет подчиненный адрес; M_SEND_XADD: мастер отправляет подчиненному расширенный адрес; M_SEND_SR: повторный запуск мастера; M_SEND_DATA: мастер отправляет данные; M_SEND_P: мастер отправляет сигнал STOP; M_RECV_DATA: мастер получает данные; ARB_LOST: Арбитраж проигран; C_IDLE: холостой ход; Рисунок 9-6. Диаграмма состояний программирования TWI.

9.1.3.5TWI Engine Master и подчиненный режим На шине TWI имеется четыре режима работы. Это Master Transmit, Master Receive, Slave Transmit и Slave. Получать. В общем, центральный процессор управляет движком TWI, записывая команды и данные в свои регистры. Механизм TWI передает прерывание на ЦП, когда каждый раз выполняется передача байта или обнаруживается команда START / STOP. Хост ЦП также может запрашивать текущий статус в регистре состояния, если механизм прерывания не отключен хостом ЦП. Когда центральный процессор ЦП хочет начать передачу данных по шине, он инициирует запуск шины, чтобы войти в режим ведущего, установив бит IM_STA в регистре TWI_CNTR на высокий уровень (прежде чем он должен быть низким). Механизм TWI будет утверждать строку INT и INT_FLAG, чтобы указать завершение команды START и каждой последующей передачи байта. При каждом прерывании микропроцессор должен проверять регистр TWI_STAT на предмет текущего состояния. Передача должна быть завершена командой STOP, установив бит M_STP в высокий уровень. В режиме Slave механизм TWI также постоянно производит выборку шины и ищет свой собственный адрес подчиненного устройства во время циклов адресации. Как только совпадение найдено, оно адресуется и прерывает хост ЦП с соответствующим статусом. По запросу хост ЦП должен прочитать статус, прочитать / записать регистр данных TWI_DATA и установить регистр управления TWI_CNTR. После каждой передачи байта ведомое устройство всегда останавливает работу удаленного ведущего устройства, удерживая следующий низкий импульс на линии SCL, пока микропроцессор не ответит на состояние предыдущей передачи байта или команду START.

9.1.4. Рекомендации по программированию Контроллер TWI работает с 8-битным форматом данных. Данные в строке TWI_SDA всегда имеют длину 8 бит. Сначала контроллер TWI отправит условие запуска. В 7-битном формате адресации TWI отправляет одно 8-битное сообщение, которое включает в себя адрес подчиненного устройства 7 MSB и 1 флаг чтения / записи LSB. Наименее значимый адрес мазка указывает направление передачи. Когда TWI работает в режиме 10-битного адреса ведомого устройства, операция будет разделена на два этапа, подробности операции см. В описании регистра в разделах 9.1.6.1 и 9.1.6.2.

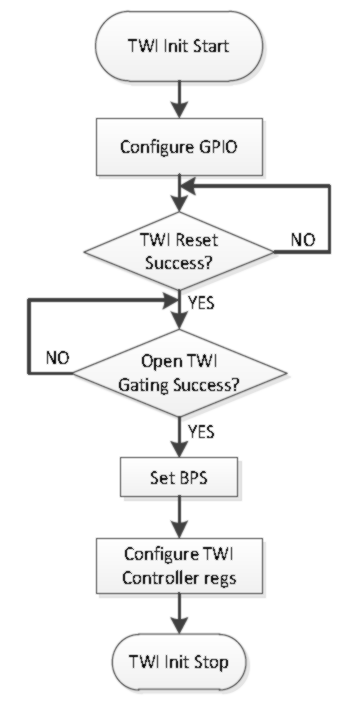

9.1.4.1Инициализация Чтобы инициализировать TWI, выполните следующие действия: Шаг 1 Настройте соответствующую функцию мультиплексирования GPIO как режим TWI. Шаг 2 Для TWIx установите TWI_BGR_REG [TWIx_GATING] в модуле CCU на 0, чтобы закрыть часы TWIx; Для S_TWIx установите R_TWI_BGR_REG [R_TWIx_GATING] в модуле PRCM на 0, чтобы закрыть часы R_TWIx. Шаг 3 Для TWIx установите TWI_BGR_REG [TWIx_RST] в модуле CCU на 0, затем установите на 1, чтобы сбросить TWIx; Для S_TWIx установите R_TWI_BGR_REG [R_TWIx_RST] в модуле PRCM на 0, затем установите на 1, чтобы сбросить R_TWIx. Шаг 4 Для TWIx установите TWI_BGR_REG [TWIx_GATING] в модуле CCU на 1, чтобы открыть часы TWIx; Для S_TWIx установите R_TWI_BGR_REG [R_TWIx_GATING] в модуле PRCM на 1, чтобы открыть часы R_TWIx. Шаг 5 Настройте TWI_CCR [CLK_M] и TWI_CCR [CLK_N], чтобы получить необходимую скорость (источником синхронизации TWI является APB2 или APBS2). Шаг 6 Настройте TWI_CNTR [BUS_EN] и TWI_CNTR [A_ACK], при использовании прерывания установите TWI_CNTR [BUS_EN] на 1 и зарегистрируйте системное прерывание через модуль GIC. В ведомом режиме настройте регистры TWI_ADDR и TWI_XADDR, чтобы завершить настройку инициализации TWI. Для PRCM см. Описание в H616_PRCM_Specification. На рисунке 9-7 показан процесс инициализации TWI. Рисунок 9-7. Процесс инициализации TWI.

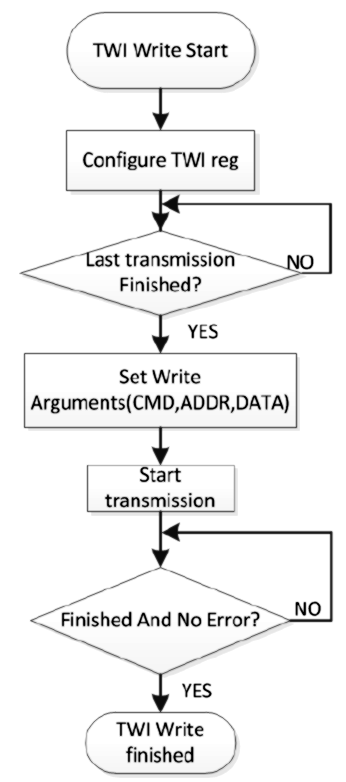

9.1.4.2Операция записи данных Чтобы записать данные на устройство, выполните следующие действия: Шаг 1 Очистите регистр TWI_EFR и настройте TWI_CNTR [M_STA] на 1 для передачи сигнала START. Шаг 2 После передачи сигнала СТАРТ запускается первое прерывание, затем записывается идентификатор устройства в TWI_DATA (для 10-разрядного идентификатора устройства сначала запишите идентификатор первого байта, затем запишите идентификатор второго байта в следующем прерывании). Шаг 3 Прерывание запускается снова после завершения передачи идентификатора устройства, запишите адрес данных устройства для чтения в TWI_DATA (для 16-битного адреса сначала запишите адрес первого байта, затем запишите адрес второго байта). Шаг 4 Прерывание запускается после завершения передачи адреса данных, данные записи должны быть переданы в TWI_DATA (для последовательной операции записи данных завершение передачи каждого байта вызывает прерывание, во время прерывания запись следующего байта данных в TWI_DATA). Шаг 5 После завершения передачи запишите TWI_CNTR [M_STP] в 1, чтобы передать сигнал STOP и завершить эту операцию записи. На рисунке 9-8 показан процесс записи TWI на устройство. Рисунок 9-8. Процесс записи данных TWI

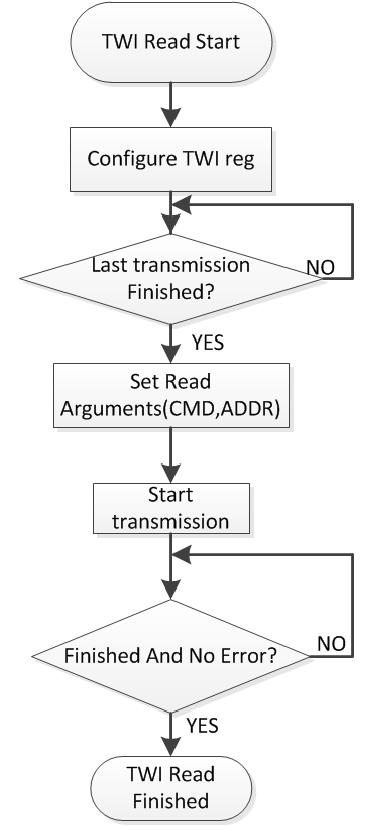

9.1.4.3Операция чтения данных Чтобы прочитать данные с устройства, выполните следующие действия: Шаг 1 Очистите регистр TWI_EFR, установите TWI_CNTR [A_ACK] в 1 и сконфигурируйте TWI_CNTR [M_STA] в 1 для передачи сигнала START. Шаг 2 После передачи сигнала СТАРТ запускается первое прерывание, затем записывается идентификатор устройства в TWI_DATA (для 10-разрядного идентификатора устройства сначала запишите идентификатор первого байта, затем запишите идентификатор второго байта в следующем прерывании). Шаг 3 Прерывание запускается снова после завершения передачи идентификатора устройства, запишите адрес данных устройства для чтения в TWI_DATA (для 16-битного адреса сначала запишите адрес первого байта, затем запишите адрес второго байта). Шаг 4 Прерывание запускается после завершения передачи адреса данных, запишите TWI_CNTR [M_STA] в 1 для передачи нового сигнала START, а после срабатывания прерывания запишите идентификатор устройства в TWI_DATA, чтобы начать операцию чтения. Шаг 5 После завершения передачи адреса устройства каждое завершение приема запускает прерывание, в свою очередь, чтение TWI_DATA для получения данных, при приеме предыдущего прерывания данных последнего байта сбрасывает TWI_CNTR [A_ACK], чтобы остановить сигнал подтверждения последнего байта. Шаг 6 Запишите TWI_CNTR [M_STP] в 1 для передачи сигнала STOP и завершения этой операции чтения. На рисунке 9-9 показан процесс чтения TWI с устройства. Рисунок 9-9. Процесс чтения данных TWI

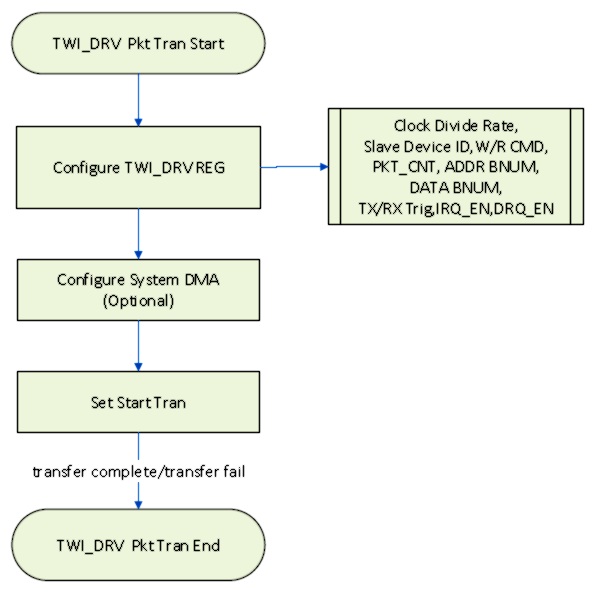

9.1.4.4Пакетная передача На рисунке 9-10 показана последовательность операций программного обеспечения для передачи пакетов драйвером TWI. Рисунок 9-10. Процесс передачи пакетов драйвером TWI

Примечания Для 7-битной адресации: SLA6 - SLA0 - это 7-битный адрес TWI в ведомом режиме. Когда TWI получает этот адрес после условия START, он генерирует прерывание и переходит в подчиненный режим. (SLA6 соответствует первому биту, полученному от шины TWI.) Если GCE установлен в «1», TWI также распознает общий адрес вызова (00h). Для 10-битной адресации: Когда полученный адрес начинается с 11110b, TWI распознает его как первую часть 10-битного адреса, и если следующие два бита совпадают с ADDR [2: 1] (т.е. SLAX9 и SLAX8 расширенного адреса устройства), он отправляет ACK. (В этот момент устройство не генерирует прерывание.) Если следующий байт адреса совпадает с регистром XADDR (SLAX7 - SLAX0), TWI генерирует прерывание и переходит в подчиненный режим.

|

|