|

Глава 9. Интерфейсы - Interfaces

Раздел 9.10. Контроллер транспортного потока - Transport Stream Controller (TSC)

9.10. TSC

9.10.1. Обзор Контроллер транспортного потока (TSC) отвечает за демультиплексирование и предварительную обработку входных мультимедийных данных, определенных в ISO / IEC 13818-1. Контроллер транспортного потока принимает поток мультимедийных данных от входов SSI (синхронный последовательный порт) / SPI (синхронный параллельный порт) и демультиплексирует данные в пакеты по PID (идентификация пакета). Прежде чем пакет будет сохранен в памяти с помощью DMA, он может быть предварительно обработан дескремблером транспортного потока. Контроллер транспортного потока может использоваться практически для всех случаев мультимедийных приложений, например: DVB Set top Box, IPTV, Streaming-media Box, мультимедийные проигрыватели и так далее. Особенности: Поддерживает интерфейс SPI / SSI, параметры синхронизации интерфейса настраиваются 32 канала ПИД-фильтра для каждого TSF Поддерживает формат пакетов нескольких транспортных потоков (188, 192, 204) Аппаратное обнаружение ошибок синхронного байта пакетов Аппаратное обнаружение пакетов PCR 64x16-битный FIFO для TSG, 64x32-битный FIFO для TSF Настраиваемый генератор транспортного потока SPI для потоков в памяти DRAM Поддерживает дескремблер DVB-CSA V1.1, DVB-CSA V2.1

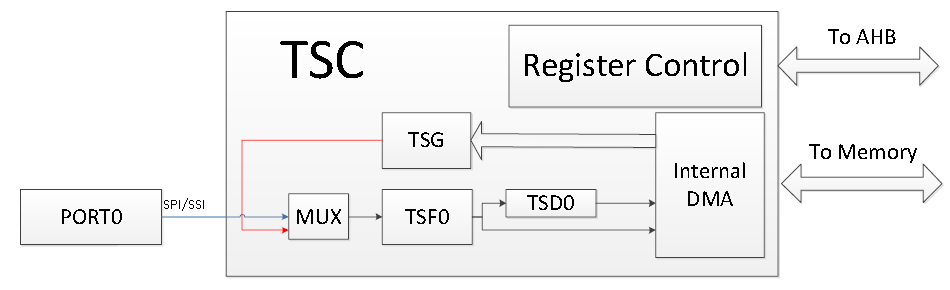

9.10.2. Блок-схема На рисунке 9-58 показана блок-схема TSC. Рисунок 9-58 Блок-схема TSC TSC - TS Controller; TSF - TS фильтр; ТСД - Дескремблер ТС; TSG - Генератор TS

9.10.3. Операции и функциональное описание

9.10.3.1Внешние сигналы В Табл. 9-26 описаны внешние сигналы TSC. Таблица 9-26. Внешние сигналы TSC Сигнал Описание Тип TS_CLK Часы ввода данных SPI / SSI I TS_ERR Ошибка указывает I TS_SYNC Пакетная синхронизация (или флаг запуска) для пакета TS I TS_DVLD Флаг достоверности данных для ввода данных TS I TS_D [7: 0] Ввод данных TS I Данные [7: 0] используются в режиме SPI; в режиме SSI используются только данные [0].

9.10.3.2Источники синхронизации В следующей таблице описаны источники синхронизации TSC. Таблица 9-27. Источники тактовых сигналов TSC OSC24M Кристалл 24 МГц PLL_PERIPH0 (1X) Периферийные часы, значение по умолчанию - 600 МГц.

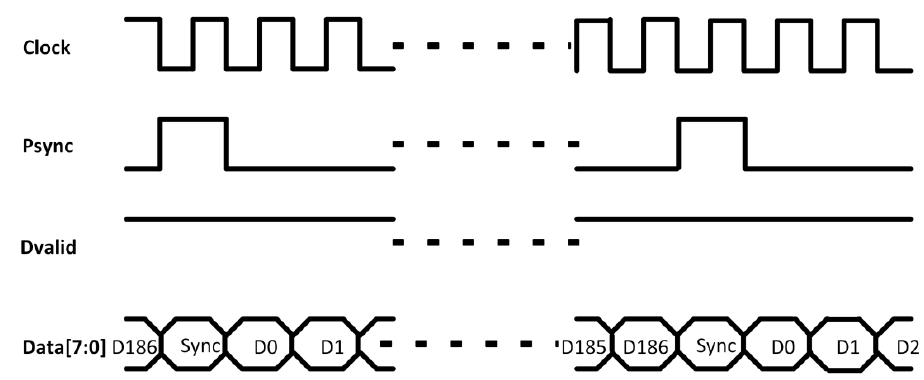

9.10.3.3Временная диаграмма Рисунок 9-59. Время ввода для режима SPI CLOCK= нарастающий фронт, PSYNC = высокий уровень активности, DVALID = высокий уровень активности, размер пакета = 188 байт)

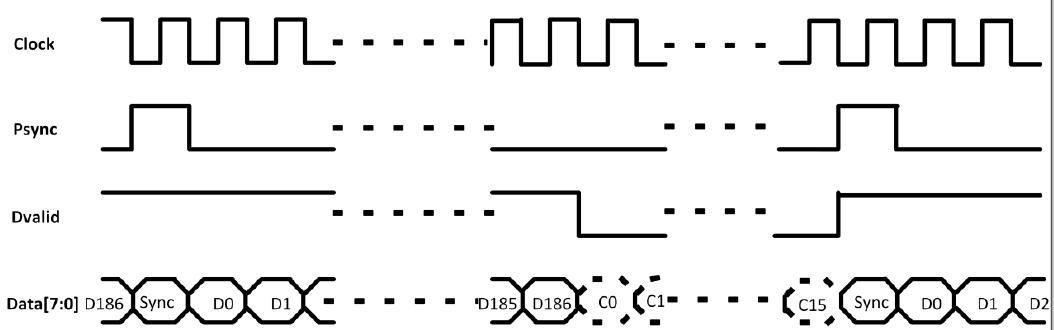

Рисунок 9-60. Альтернативное время ввода для режима SPI (Clock = нарастающий фронт, PSYNC = высокий уровень активности, DVALID = высокий уровень активности, размер пакета = 188 байт)

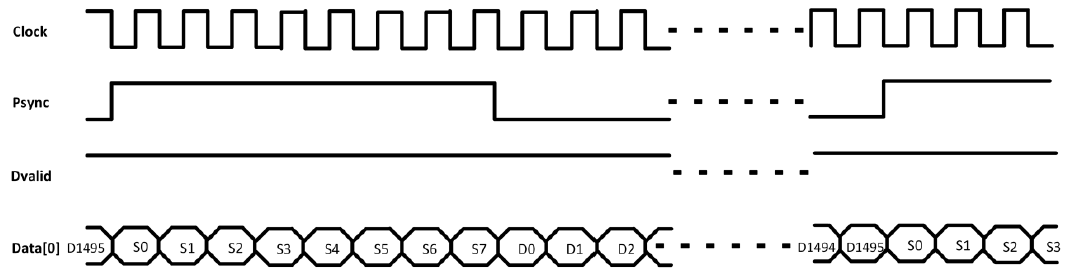

Рисунок 9-61. Альтернативное время входа для режима SSI (Clock = нарастающий фронт, PSYNC = высокий уровень активности, DVALID = высокий уровень активности, размер пакета = 188 байт)

9.10.4. Рекомендации по программированию

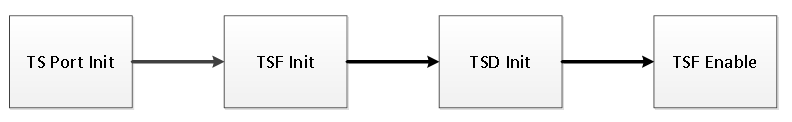

9.10.4.1Инициализация TS Port Init Рисунок 9-62. Инициализация TSC PID, DMA ADDR, DMA SIZE, Write Pointer, Read Pointer Register для TSF должны сначала очиститься до 0 после включения питания.

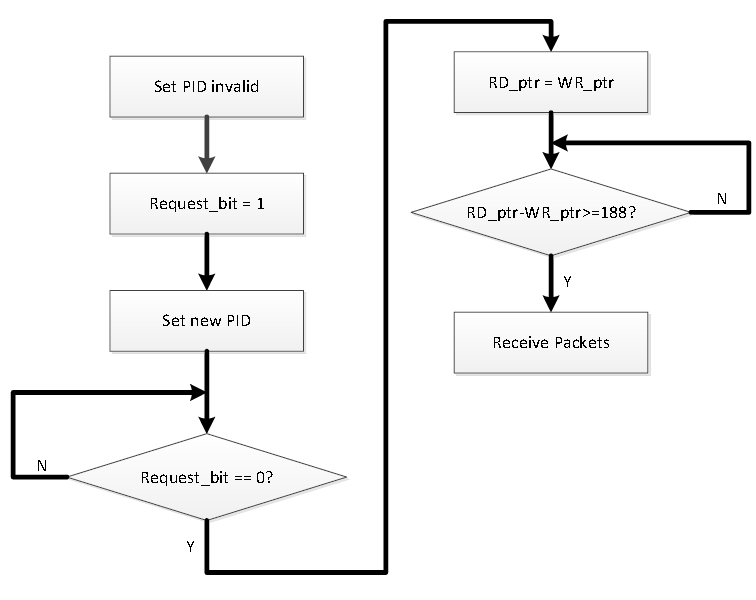

9.10.4.2Изменение PID Рисунок 9-63. Изменение ПИД-регулятора Примечание Request_bit - это 8-й бит регистра управления и состояния TSF.

|

|