9. Интерфейсы (Interfaces)

9.10. Контроллер транспортного потока

9.2. Универсальный асинхронный приемо-передатчик

9.3. Синхронный последовательный интерфейс

9.4. USB 2.0 OTG

9.6. Контроллер порта

9.7. Низкоскоростной АЦП

9.9. Контроллер ШИМ

Глава 9. Интерфейсы - Interfaces

Раздел 9.4. USB 2.0 OTG - USB 2.0 OTG ("On-the-Go")

9.4. USB2.0 OTG

9.4.1. Обзор

USB2.0 OTG - это контроллер устройства с двумя ролями, который поддерживает функции устройства и хоста, который также может быть настроен как контроллер только для хоста или только для устройства, полностью соответствующий спецификации USB2.0. Он может поддерживать высокоскоростную (HS, 480 Мбит / с), полную (FS, 12 Мбит / с) и низкоскоростную (LS, 1,5 Мбит / с) передачу в режиме хоста. Он может поддерживать высокую скорость (HS, 480 Мбит / с) и полную скорость (FS, 12 Мбит / с) в режиме устройства. Стандартный USB-трансивер можно использовать через интерфейс UTMI + PHY Level3. Интерфейс UTMI + PHY является двунаправленным с 8-битной шиной данных. Для экономии пропускной способности ЦП интерфейс USB-OTG DMA может поддерживать внешний контроллер DMA, обеспечивающий передачу данных между памятью и USB-OTG FIFO. Ядро USB-OTG также поддерживает функции энергосбережения USB. USB2.0 OTG имеет следующие особенности:9.4.2. Блок-схема

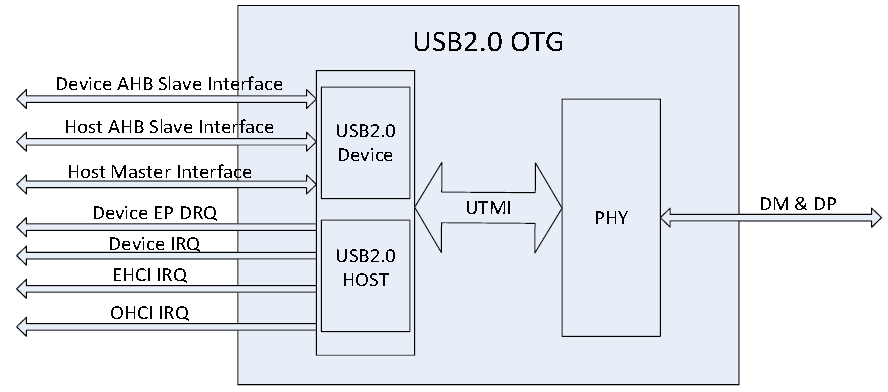

На рисунке 9-29 показана блок-схема контроллера USB2.0 OTG.

9.4.3. Операции и функциональные описания

9.4.3.1

Внешние сигналы

Таблица 9-12. Внешние сигналы USB2.0 OTGСигнал Описание Тип

9.4.3.2

Схема подключения контроллера PHY

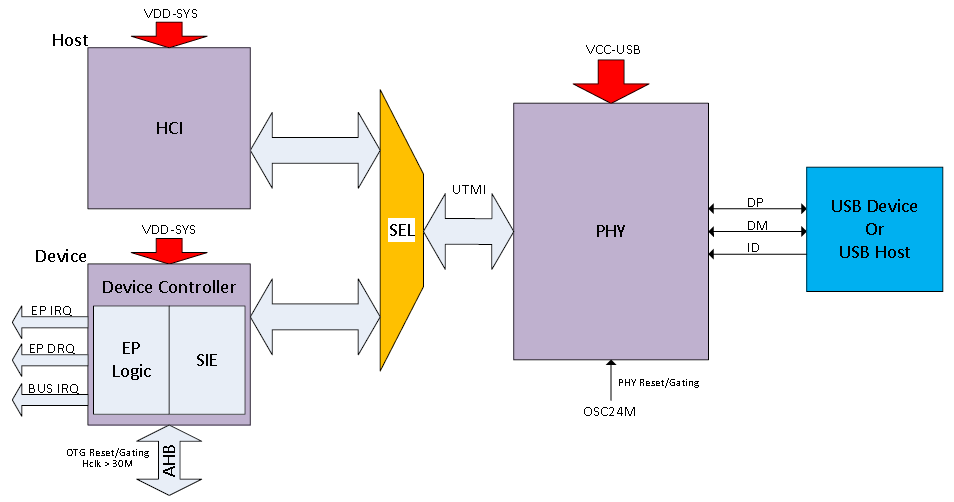

Рисунок 9-30. Контроллер USB2.0 OTG и схема подключения контроллера физического уровня.