|

Глава 9. Интерфейсы - Interfaces

Раздел 9.2. Универсальный асинхронный приемо-передатчик - Universal Asynchronous Receiver Transmitter (UART)

9.2. UART

9.2.1. Обзор UART используется для последовательной связи с периферийным устройством, модемом (оборудование носителя данных, DCE) или набором данных. Данные записываются из главного (ЦП) по шине APB в UART, преобразуются в последовательную форму и передаются на устройство назначения. Последовательные данные также принимаются UART и сохраняются для главного (ЦП) для чтения. UART содержит регистры для управления длиной символа, скоростью передачи, генерацией / проверкой четности и генерацией прерывания. Хотя есть только один выходной сигнал прерывания от UART, есть несколько приоритетных типов прерываний, которые могут быть ответственны за его утверждение. Каждый из типов прерываний можно отдельно включать / отключать с помощью регистров управления. UART имеет режимы работы 16450 и 16550, которые совместимы с рядом стандартных программных драйверов. В режиме 16550 операции передачи и приема буферизуются с помощью FIFO. В режиме 16450 эти FIFO отключены. UART поддерживает длину слова от пяти до восьми битов, дополнительный бит четности и 1, 1 ? или 2 стоповых бита и полностью программируется с помощью интерфейса ЦП AMBA APB. В комплект входят 16-битный программируемый генератор скорости передачи и 8-битный рабочий регистр, а также отдельные FIFO для передачи и приема. Предусмотрено восемь линий управления модемом и диагностический шлейфовый режим. Прерывания могут быть сгенерированы для ряда условий буфера TX / FIFO, буфера RX / FIFO, состояния модема и состояния линии. Для интеграции в систему, где требуется формат последовательных данных инфракрасного SIR, UART может быть сконфигурирован для использования программно-программируемого режима IrDA SIR. Если этот режим не выбран, доступен только формат последовательных данных UART (стандарт RS232). UART имеет следующие особенности: До 6 контроллеров UART (UART0, UART1, UART2, UART3, UART4, UART5) UART0, UART5: 2-проводный; UART1, UART2, UART3, UART4: 4-проводный 2-проводной UART можно использовать для печати; 4-проводной UART можно использовать для управления потоком Совместимость со стандартными 16550 UART 256 байтов FIFO для передачи и приема данных Обеспечивает скорость до 4 Мбит / с с тактовой частотой APB 64 МГц и скорость до 1,5 Мбит / с с тактовой частотой APB 24 МГц Поддерживает от 5 до 8 бит данных и 1 / 1,5 / 2 стоповых бит Поддерживает четность, нечетность или отсутствие четности Поддерживает интерфейс контроллера DMA Поддерживает программное / аппаратное управление потоком данных Поддерживает IrDA 1.0 SIR Поддерживает RS-485/9-битный режим

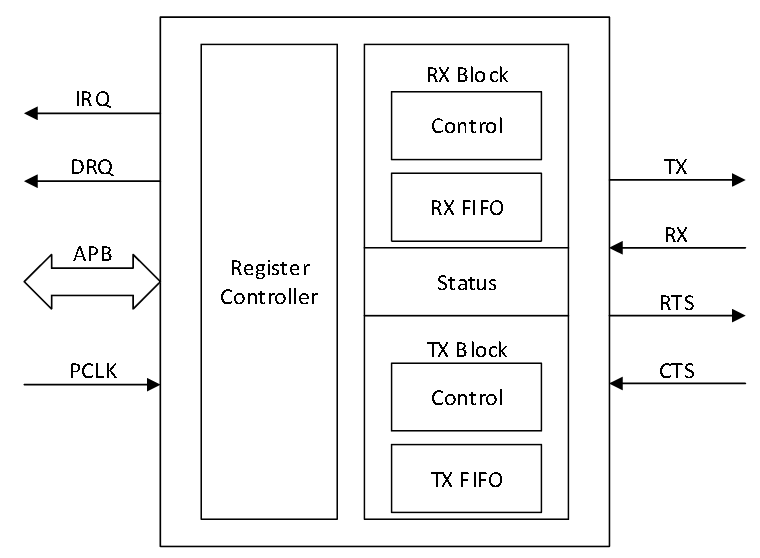

9.2.2. Блок-схема На рисунке 9-11 показана блок-схема UART. Рисунок 9-11. Блок-схема UART

9.2.3. Операции и функциональные описания

9.2.3.1Внешние сигналы В Табл. 9-3 описаны внешние сигналы UART. Таблица 9-3. Внешние сигналы UART Тип сигнала Описание UART0_TX O UART0 Передача данных UART0_RX I Прием данных UART0 UART1_TX O UART1 Передача данных UART1_RX I Прием данных UART1 UART1_CTS I Данные UART1 очищены для отправки UART1_RTS O UART1 Запрос данных для отправки UART2_TX O UART2 Передача данных UART2_RX I Прием данных UART2 UART2_CTS I Данные UART2 очищены для отправки UART2_RTS O Запрос данных UART2 для отправки UART3_TX O UART3 Передача данных UART3_RX I Прием данных UART3 UART3_CTS I Данные UART3 очищены для отправки UART3_RTS O Запрос данных UART3 для отправки UART4_TX O UART4 Передача данных UART4_RX I Прием данных UART4 UART4_CTS I Данные UART4 очищены для отправки UART4_RTS O Запрос данных UART4 для отправки UART5_TX O UART5 Передача данных UART5_RX I Прием данных UART5

9.2.3.2Источники синхроимпульсов В Табл. 9-4 описаны источники тактовой частоты UART. Таблица 9-4. Источники тактовой частоты UART Источники синхроимпульсов Описание APB2_CLK Часы APB2

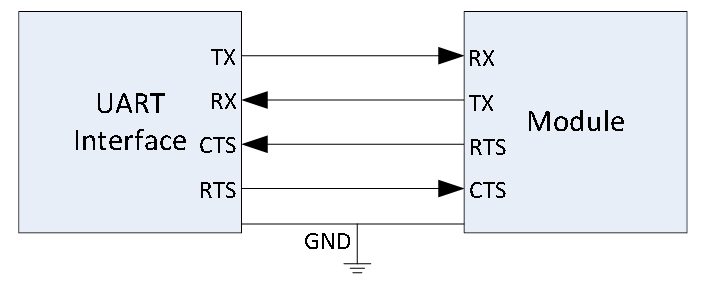

9.2.3.3Типичное применение На рисунке 9-12 показана блок-схема приложения UART. Рисунок 9-12. Схема приложения UART.

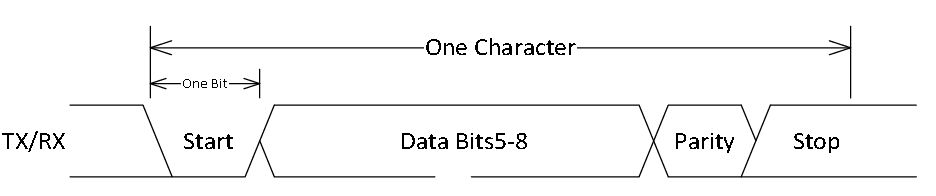

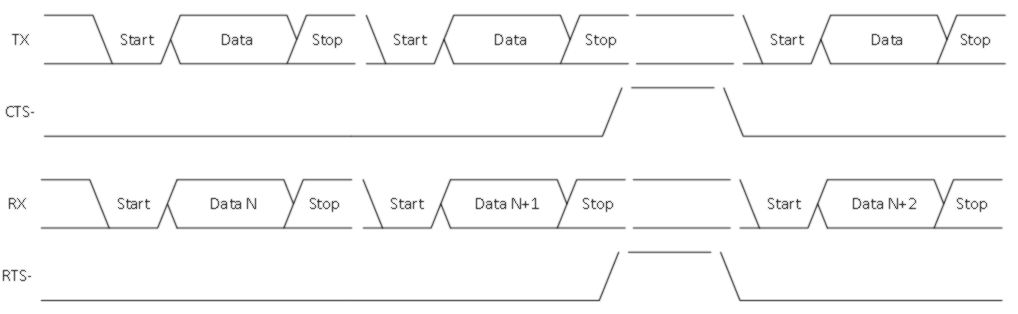

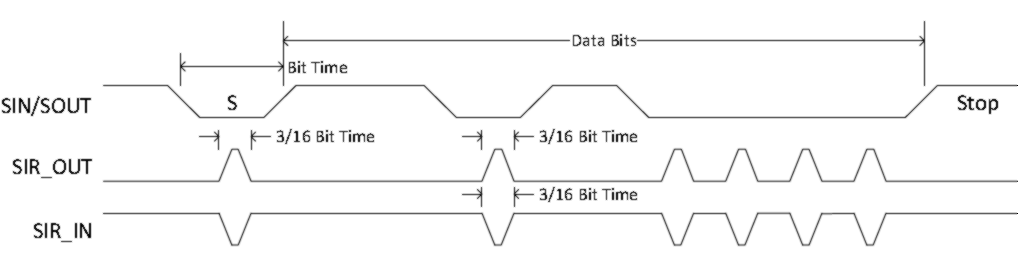

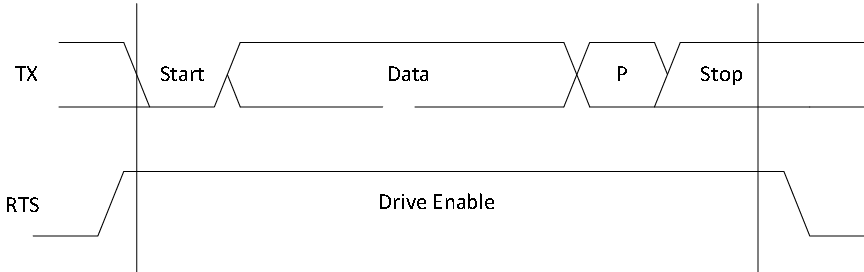

9.2.3.4Временная диаграмма UART Рисунок 9-13. Формат последовательных данных UART. Рисунок 9-14. Время управления автоматическим потоком RTS / CTS. Рисунок 9-15. Формат данных последовательного IrDA. Рисунок 9-16. Синхронизация RS-485.

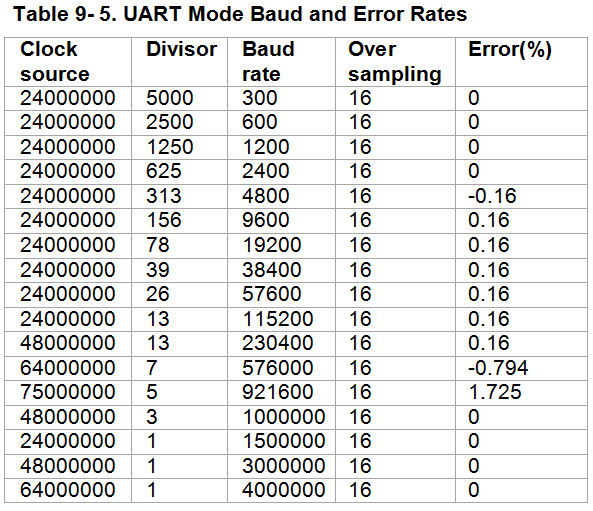

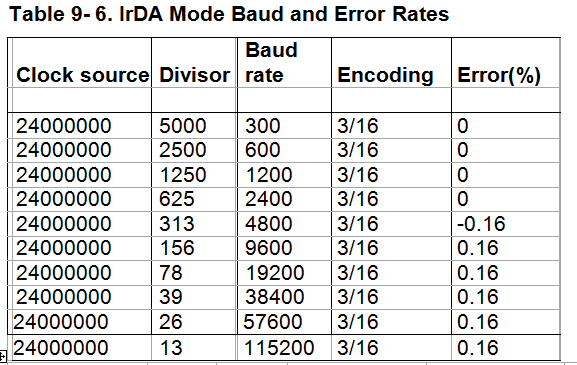

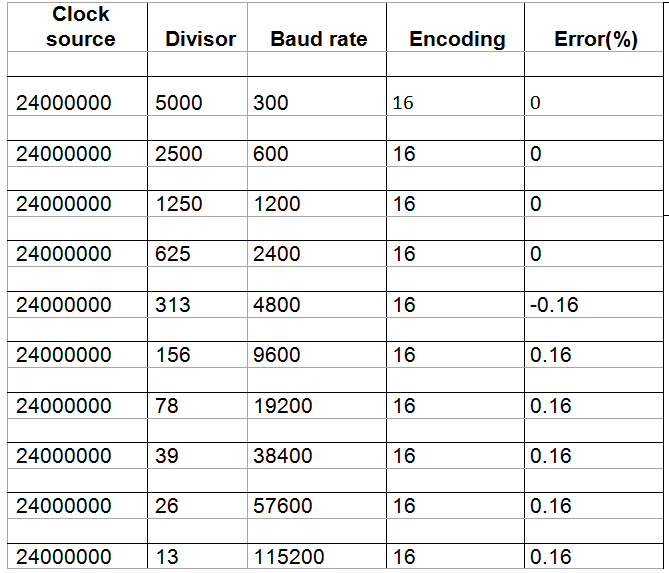

9.2.3.5Режим работы UART 1. Настройка базового режима Регистр UART_LCR может устанавливать основные параметры кадра данных: ширину данных (от 5 до 8 бит), количество стоповых битов (1 / 1,5 / 2), тип четности. Передача кадра UART включает в себя сигнал запуска, сигнал данных, бит четности и сигнал остановки. LSB передается первым. Стартовый сигнал (стартовый бит): это флаг начала кадра данных. Согласно протоколу UART, низкий уровень сигнала TXD указывает на начало кадра данных. Когда UART передает данные, уровень должен оставаться высоким. Сигнал данных (бит данных): Разрядность данных может быть сконфигурирована как 5-битная, 6-битная, 7-битная, 8-битная через различные приложения. Бит четности: это 1-битовый сигнал коррекции ошибок. Бит четности включает нечетную четность, четность. UART может включать и отключать бит четности, задав регистр UART_LCR. Стоп-сигнал (стоповый бит): это стоповый бит кадра данных. Стоп-бит может быть установлен в 1, 1,5 и 2 бита регистром UART_LCR. Высокий уровень сигнала TXD указывает на конец кадра данных. 2. Настройка скорости передачи Скорость передачи рассчитывается следующим образом: Скорость передачи = SCLK / (16 * делитель). SCLK обычно APB2 и может быть установлен в CCU. Divisor - это делитель частоты UART. Делитель частоты имеет 16 бит, младшие 8 бит находятся в регистре UART_DLL, старшие 8 бит находятся в регистре UART_DLH. Связь между различными режимами UART и частотой ошибок следующая. Таблица 9-5. Скорость передачи в бодах и ошибок в режиме UART Таблица 9-6. Скорость передачи данных и ошибок в режиме IrDA Таблица 9-7. Скорость передачи данных в режиме RS485 и частота ошибок 3. Настройка DLAB Бит управления DLAB (UART_LCR [7]) - это бит управления доступом регистра фиксации делителя. Если DLAB равен 0, то адрес смещения 0x00 - это регистр TX / RX FIFO, адрес смещения 0x04 - это регистр IER. Если DLAB равен 1, то адрес смещения 0x00 - это регистр DLL, адрес смещения 0x04 - это регистр DLH. При инициализации UART необходимо установить делитель. То есть запись 1 в DLAB может получить доступ к регистрам DLL и DLH, после завершения настройки запись 0 в DLAB может получить доступ к регистру TX / RX FIFO. 4. Настройка CHCFG_AT_BUSY Функции CHCFG_AT_BUSY (UART_HALT [1]) и CHANGE_UPDATE (UART_HALT [2]) заключаются в следующем. CHCFG_AT_BUSY (настроить при занятости): включить бит, программное обеспечение также может установить контроллер UART, когда UART занят, например регистр LCR, DLH, DLL. CHANGE_UPDATE (обновить конфигурацию): если CHCFG_AT_BUSY включен, а CHANGE_UPDATE записано в 1, конфигурация контроллера UART может быть обновлена. После завершения обновления бит автоматически сбрасывается в 0. Установка делителя выполняет следующие действия: Шаг 1 Запишите 1 в CHCFG_AT_BUSY, чтобы разрешить настройку при занятости. Шаг 2 Запишите 1 в DLAB и установите DLH и DLL. Шаг 3 Запишите 1 в CHANGE_UPDATE, чтобы обновить конфигурацию. После завершения бит автоматически сбрасывается в 0. 5. UART занят UART_USR [0] - это флаг занятости контроллера UART или нет. Когда TX передает данные, или RX принимает данные, или TX FIFO не пуст, или RX FIFO не пуст, тогда бит флага BUSY может быть установлен в 1 аппаратно, что указывает на то, что контроллер UART занят.

9.2.4. Рекомендации по программированию

9.2.4.1Инициализация Шаг 1 Инициализация системы Настройте APB2_CFG_REG в модуле CCU, чтобы установить тактовую частоту шины APB2 (по умолчанию частота составляет 24 МГц). Установите UART_BGR_REG [UARTx_GATING] в 1, чтобы включить часы модуля, и установите UART_BGR_REG [UARTx_RST] в 1, чтобы отключить модуль. Шаг 2 Инициализация контроллера UART Конфигурация ввода-вывода: настройте мультиплексор GPIO как функцию UART и установите контакты UART во внутренний подтягивающий режим (подробности см. В описании в разделе «Контроллер порта»). Конфигурация скорости передачи: Установите скорость передачи UART (см. п. 9.2.3.5.2); Запишите UART_FCR [FIFOE] в 1, чтобы включить TX / RX FIFO; Запишите UART_HALT [HALT_TX] в 1, чтобы отключить передачу TX; Установите UART_LCR [DLAB] в 1, оставьте конфигурацию по умолчанию для других битов; установить адрес смещения 0x00 в регистр UART_DLL, установить адрес смещения 0x04 в регистр UART_DLH; Запишите старшие 8 бит делителя в UART_DLH, а младшие 8 бит делителя в UART_DLL; Установите UART_LCR [DLAB] на 0, оставьте конфигурацию по умолчанию для других битов; установить адрес смещения 0x00 в регистр UART_RBR / UART_THR, установить адрес смещения 0x04 в регистр UART_IER; Установите UART_HALT [HALT_TX] на 0, чтобы разрешить передачу TX. Шаг 3 Конфигурация параметров контроллера Установите ширину данных, стоповые биты и тип четности / нечетности, записав регистр UART_LCR. Сбросьте, включите FIFO и установите условие запуска FIFO, записав регистр UART_FCR. Установите параметр управления потоком, записав регистр UART_MCR. Шаг 4 Конфигурация прерываний Настройте номер вектора прерывания UART для запроса прерывания UART (номер вектора прерывания см. В модуле GIC). В режиме DMA запишите UART_IER в 0, чтобы отключить прерывание; запишите UART_HSK [Конфигурация рукопожатия] в 0xE5, чтобы установить режим рукопожатия DMA; запишите UART_FCR [DMAM] в 1, чтобы установить режим передачи / приема DMA; установить параметр DMA и запросить прерывание DMA в соответствии с процессом настройки DMA. В режиме прерывания настройте UART_IER для включения соответствующего прерывания в соответствии с требованиями: например, прерывание передачи (TX), прерывание приема (RX), прерывание состояния линии приема, прерывание RS48 и т.д. (Здесь обычно используется прерывание TX / RX).

9.2.4.2Передача / прием данных в режиме запроса Обмен данными Шаг 1 Запишите данные в UART_THR, чтобы начать передачу данных. Шаг 2 Проверьте статус TX_FIFO, прочитав UART_USR [TFNF]. Если бит равен 1, данные можно продолжать записывать; если бит равен 0, дождитесь передачи данных, и данные не могут продолжать запись, пока FIFO не заполнится. Получение данных Шаг 1 Проверьте статус RX_FIFO, прочитав UART_USR [RFNE]. Шаг 2 Считайте данные из UART_RBR, если RX_FIFO не пуст. Шаг 3 Если UART_USR [RFNE] равен 0, данные принимаются полностью.

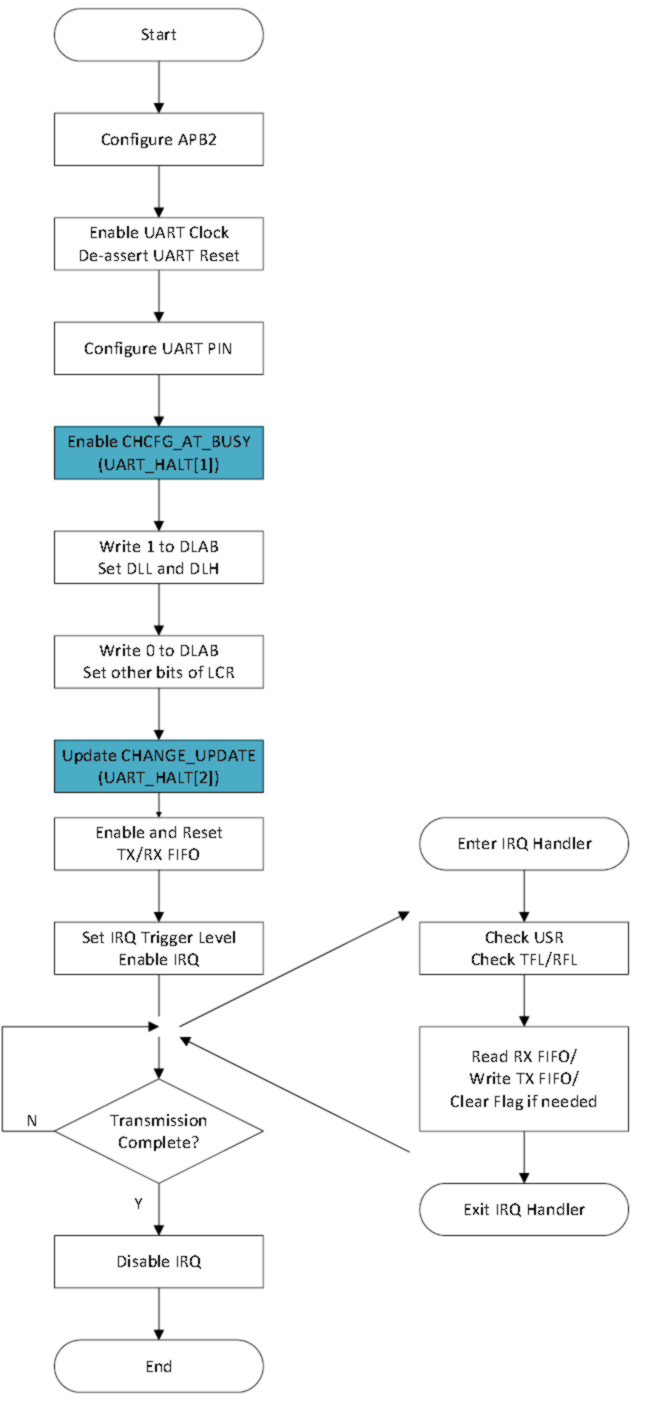

9.2.4.3Передача / получение данных в режиме прерывания Обмен данными Шаг 1 Установите UART_IER [ETBEI] в 1, чтобы разрешить прерывание передачи UART. Шаг 2 Запишите данные для передачи в UART_THR. Шаг 3 Когда данные TX_FIFO удовлетворяют условию запуска (например, FIFO / 2, FIFO / 4), генерируется прерывание передачи UART. Шаг 4 Проверьте UART_USR [TFE] и определите, пуст ли TX_FIFO. Если UART_USR [TFE] равен 1, это означает, что данные в TX_FIFO переданы полностью. Шаг 5 Сбросьте UART_IER [ETBEI] в 0, чтобы отключить прерывание передачи. Получение данных Шаг 1 Установите UART_IER [ERBFI] на 1, чтобы разрешить прерывание приема UART. Шаг 2 Когда полученные данные от RX_FIFO удовлетворяют условию запуска (например, FIFO / 2, FIFO / 4), генерируется прерывание приема UART. Шаг 3 Считайте данные из UART_RBR. Шаг 4 Проверьте статус RX_FIFO, прочитав UART_USR [RFNE], и определите, следует ли читать данные. Если бит равен 1, продолжайте чтение данных из UART_RBR до тех пор, пока UART_USR [RFNE] не будет сброшен до 0, что означает, что данные получены полностью. На рис. 9-17 показан процесс передачи и приема данных UART в режиме прерывания. Рисунок 9-17. Процесс передачи / приема данных UART в режиме прерывания.

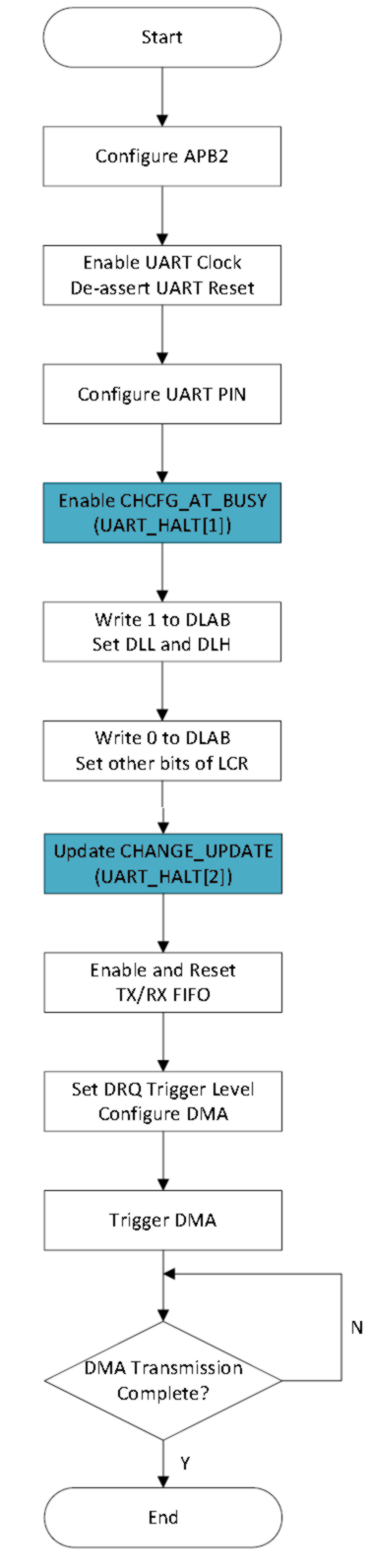

9.2.4.4Передача / получение данных в режиме DMA Обмен данными Шаг 1 Настройте прерывание DMA UART в соответствии с процессом инициализации. Шаг 2 Настройте канал данных DMA, включая адрес источника передачи, адрес назначения передачи, количество передаваемых данных, тип передачи и т.д. (Подробности см. В описании модуля DMAC). Шаг 3 Включите функцию передачи DMA UART, установив регистр модуля DMA. Шаг 4 Определите, полностью ли переданы данные UART, на основе статуса DMA. Если все данные переданы полностью, отключите функцию передачи DMA UART. Получение данных Шаг 1 Настройте канал данных DMA, включая адрес источника передачи, адрес назначения передачи, количество передаваемых данных, тип передачи и т.д. (Подробнее см. Описание в модуле DMAC). Шаг 2 Включите функцию приема DMA UART, установив регистр модуля DMA. Шаг 3 Определите, полностью ли получены данные UART, на основании статуса DMA. Если все данные получены полностью, отключите функцию приема DMA UART. На рис. 9-18 показан процесс передачи данных UART в режиме DMA. Рисунок 9-18. Процесс передачи данных DMA в режиме DMA.

|

|