9.10. Контроллер транспортного потока

9.2. Универсальный асинхронный приемо-передатчик

9.3. Синхронный последовательный интерфейс

9.4. USB 2.0 OTG

9.6. Контроллер порта

9.7. Низкоскоростной АЦП

9.9. Контроллер ШИМ

Глава 9. Интерфейсы - Interfaces

Раздел 9.7. Низкоскоростной АЦП - Low Rate ADC (LRADC)

9.7. LRADC

9.7.1. Обзор

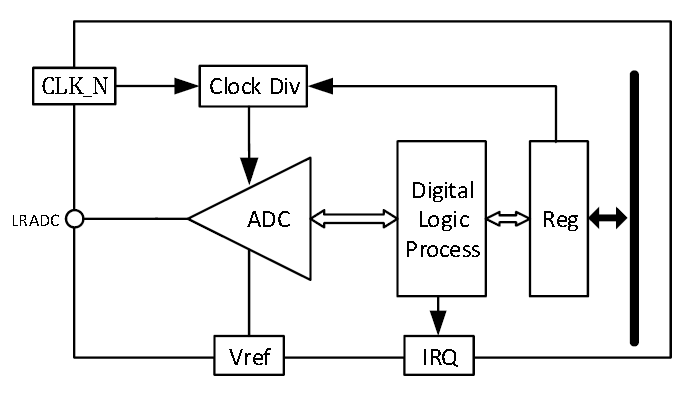

Низкоскоростной АЦП (LRADC) имеет 6-битное разрешение для ключевого приложения. LRADC может работать с максимальной частотой преобразования 2 кГц.9.7.2. Блок-схема

На рис. 9-35 показана блок-схема LRADC.

Рисунок 9-35. Блок-схема LRADC

9.7.3. Операции и функциональное описание

9.7.3.1

Внешние сигналы

Таблица 9-22 Внешний сигнал LRADC.

9.7.3.2

Источники синхроимпульсов

Таблица 9-23. Источники тактовой частоты LRADC

9.7.3.3

Режим работы LRADC

(1). Нормальный режим

АЦП собирает 8 отсчетов, среднее значение из 8 отсчетов обновляется в регистре данных, и включается знак прерывания данных. Он опрашивается повторно в соответствии с этим режимом до остановки АЦП.(2). Продолжить режим

АЦП собирает 8 выборок через каждые 8 ??* (N + 1) циклов выборки. Среднее значение каждых 8 выборок обновляется в регистре данных, и включается знак прерывания данных. (N определяется в бите [19:16] LRADC_CTRL_REG).(3) .Одиночный режим

АЦП собирает 8 отсчетов, среднее из 8 отсчетов обновляется в регистре данных, и включается знак прерывания данных, так как после этого АЦП останавливает отсчет.9.7.3.4

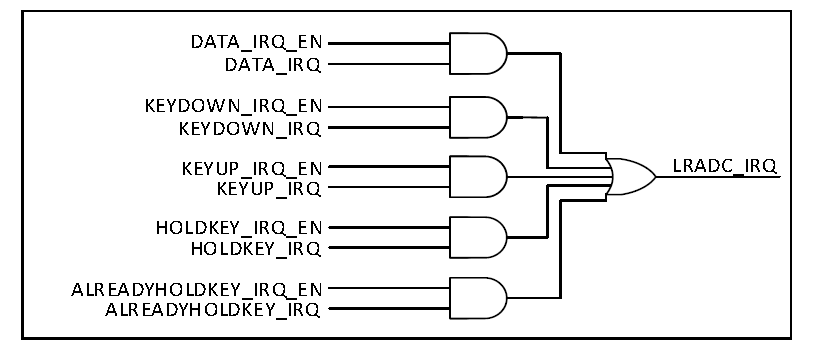

Прерывание

Каждый канал LRADC имеет пять источников прерываний и пять элементов управления разрешением прерывания.

Рисунок 9-36. Прерывание LRADC

Когда входное напряжение находится в пределах от LEVELA (1,35 В) до LEVELB (управление битом [5: 4] LRADC_CTRL), может быть сгенерировано IRQ1. Когда входное напряжение ниже LEVELB, может быть сгенерировано IRQ2.

Если контроллер получает IRQ1 и не получает IRQ2 в какой-то момент, то контроллер генерирует прерывание Hold KEY, в противном случае - прерывание DATA_IRQ.

Hold KEY обычно используется для самоблокирующегося ключа. Когда самоблокирующийся ключ сохраняет статус блокировки, контроллер получает IRQ2, затем контроллер генерирует прерывание уже удерживаемого ключа.

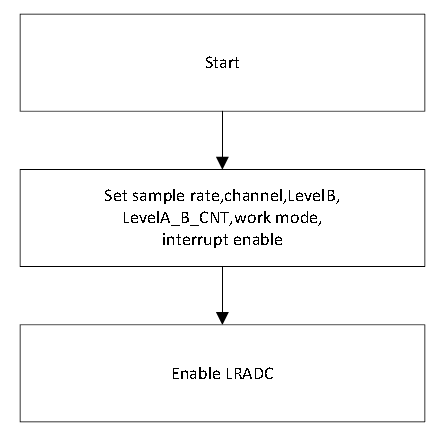

9.7.4. Рекомендации по программированию

Рисунок 9-37. Начальный процесс LRADC