9.10. Контроллер транспортного потока

9.2. Универсальный асинхронный приемо-передатчик

9.3. Синхронный последовательный интерфейс

9.4. USB 2.0 OTG

9.6. Контроллер порта

9.7. Низкоскоростной АЦП

9.9. Контроллер ШИМ

Глава 9. Интерфейсы - Interfaces

Раздел 9.3. Синхронный последовательный интерфейс - Serial Peripheral Interface (SPI)

9.3. SPI

9.3.1. Обзор

SPI - это полнодуплексный синхронный последовательный интерфейс связи, который обеспечивает быструю передачу данных с меньшим количеством программных прерываний. Контроллер SPI содержит один буфер приемника 64x8 бит (RXFIFO) и один буфер передачи 64x8 бит (TXFIFO). Он может работать в режиме ведущего и ведомого. SPI имеет следующие особенности:9.3.2. Блок-схема

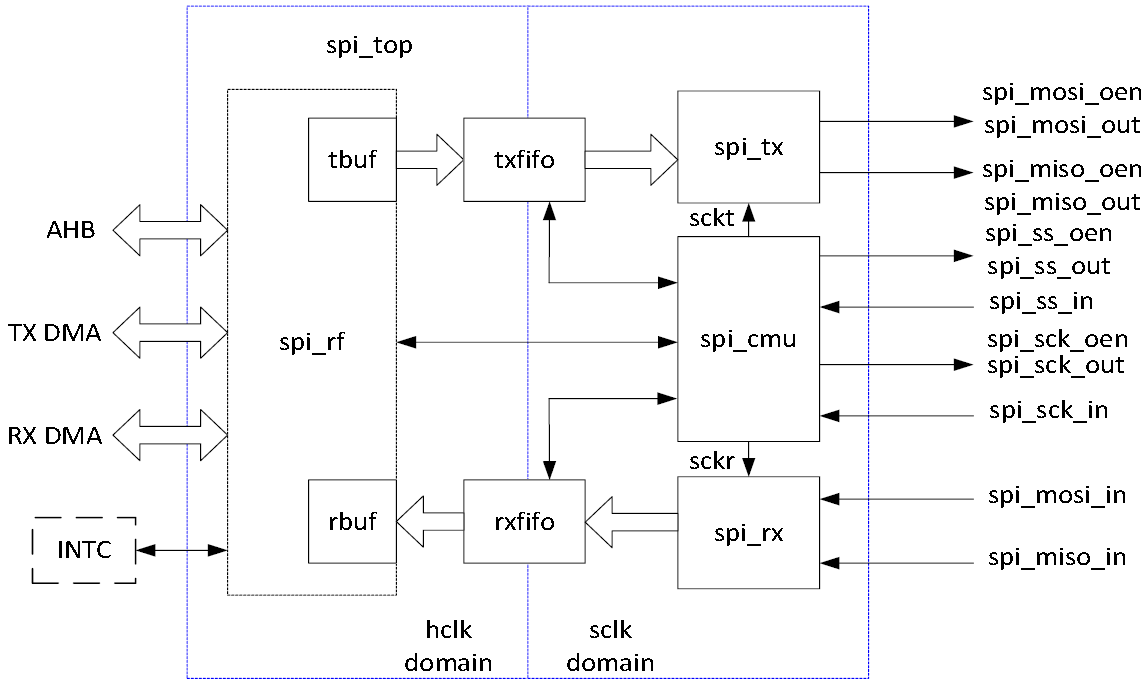

На рисунке 9-19 показана блок-схема SPI.

Рисунок 9-19. Блок-схема SPI

SPI включает:9.3.3. Операции и функциональные описания

9.3.3.1

Внешние сигналы

В Таблице 9-8 описаны внешние сигналы SPI. MOSI и MISO - это двунаправленный ввод-вывод, когда SPI настроен как ведущее устройство, CLK и CS являются выходным контактом; когда SPI настраивается как ведомое устройство, CLK и CS являются входными контактами. Неиспользуемые порты SPI используются как порты ввода-вывода общего назначения. Таблица 9-8. Внешние сигналы SPI9.3.3.2

Источники синхроимпульсов

Контроллер SPI получает 5 различных источников синхронизации, пользователи могут выбрать один из них, чтобы сделать источник синхронизации SPI. Таблица 9-9. Источники тактовой частоты SPIИсточники часов Описание

9.3.3.3

Типичное применение

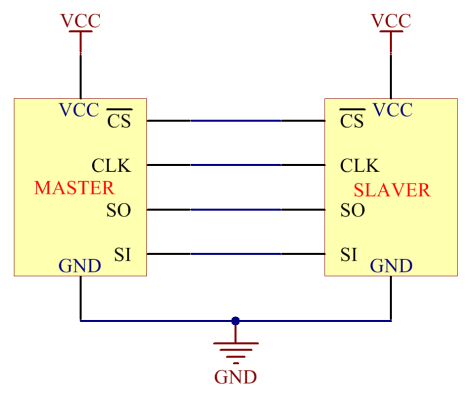

На рисунке 9-20 показана блок-схема применения, когда ведущее устройство SPI подключено к ведомому устройству.

Рисунок 9-20. Блок-схема применения SPI.

9.3.3.4

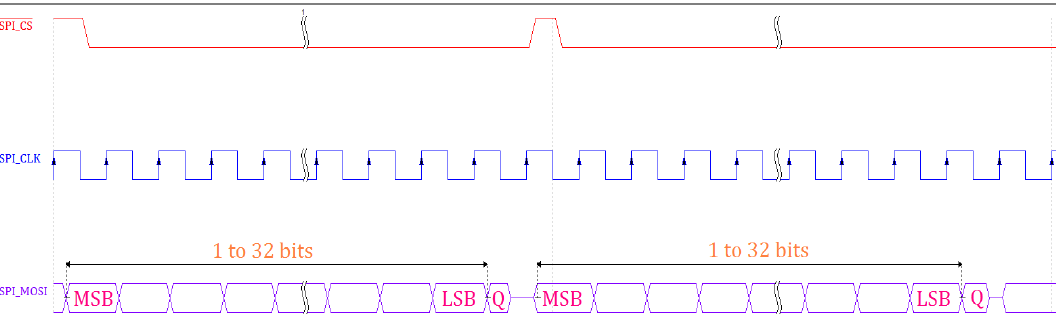

Формат передачи SPI

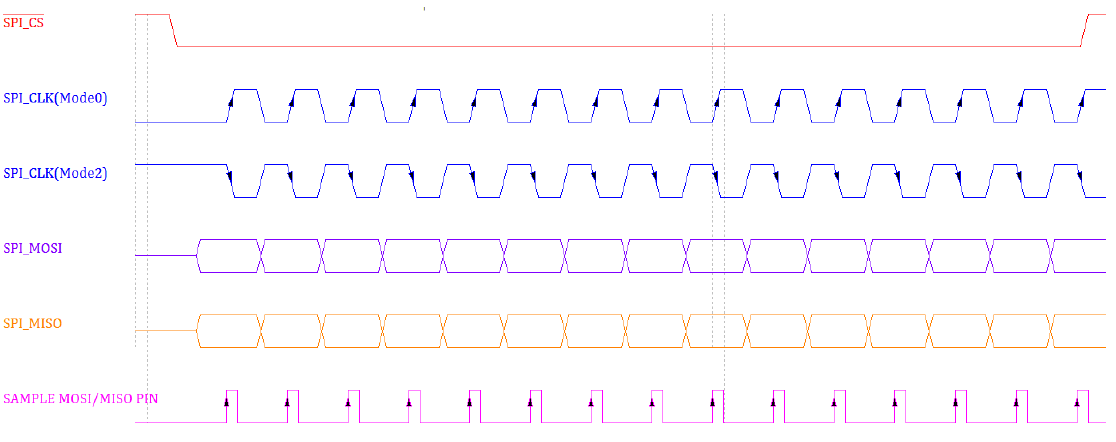

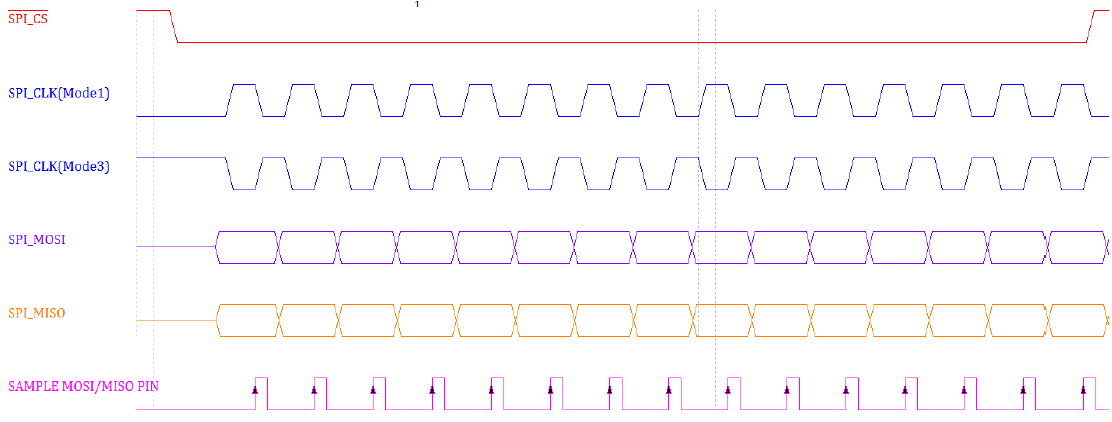

SPI поддерживает 4 различных формата передачи данных. Программное обеспечение может выбрать один из четырех режимов, в которых работает SPI, установив бит 1 (полярность) и бит 0 (фаза) регистра управления передачей SPI. Главный контроллер SPI использует сигнал SPI_SCLK для передачи данных в регистр сдвига и из него. Данные синхронизируются с использованием любой из четырех программируемых комбинаций фазы и полярности тактового сигнала. Во время операций фазы 0, полярности 0 и фазы 1, полярности 1 выходные данные изменяются по спадающему фронту тактовой частоты, а входные данные смещаются по переднему фронту. Во время операций фазы 1, полярности 0 и фазы 0, полярности 1 выходные данные изменяются по нарастающим фронтам тактового сигнала и смещаются по спадающим фронтам. POL определяет полярность сигнала, когда SPI_SCLK находится в состоянии ожидания. SPI_SCLK имеет высокий уровень, когда POL равен «1», и низкий уровень, когда POL равен «0». PHA решает, используется ли передний фронт SPI_SCLK для настройки или выборки данных. Передний фронт используется для данных настройки, когда PHA равен «1», и для данных выборки, когда PHA равен «0». Четыре режима перечислены в Таблице 9-10.Таблица 9-10. Формат передачи SPI

Режим SPI POL PHA Передний фронт Задний фронт

Рисунок 9-21. Временная диаграмма фазы 0 SPI

Рисунок 9-22. Временная диаграмма SPI фазы 1

9.3.3.5

Режим SPI Master и Slave

Контроллер SPI можно настроить как ведущее или ведомое устройство. Главный режим выбирается установкой бита MODE в Регистр глобального контроля SPI; Ведомый режим выбирается очисткой бита MODE в регистре глобального управления SPI. В ведущем режиме SPI_CLK генерируется и передается на внешнее устройство, а данные из TX FIFO передаются на вывод MOSI, данные от ведомого устройства принимаются на выводе MISO и отправляются в RX FIFO. Выбор микросхемы (SPI_SS) - активный низкий сигнал. SPI_SS должен быть установлен на низкий уровень перед передачей или приемом данных. SPI_SS может быть выбран как автоматическое управление SPI или ручное программное управление. При использовании автоматического управления SS_OWNER (бит 6 в регистре управления передачей SPI) должен быть очищен (значение по умолчанию - 0); при использовании ручного управления должен быть установлен SS_OWNER, уровень выбора чипа контролируется битом SS_LEVEL (бит 7 в регистр управления передачей SPI). В режиме ведомого, после того, как программное обеспечение устанавливает бит РЕЖИМА на «0», оно ждет, пока ведущий не инициирует транзакцию. Когда мастер утверждает, что SPI_SS и SPI_CLK передается подчиненному, данные подчиненного передаются из TX FIFO на вывод MISO, а данные с вывода MOSI принимаются в RX FIFO.9.3.3.6

3-проводной режим SPI

Трехпроводной режим SPI действителен только тогда, когда контроллер SPI работает в ведущем режиме, и выбирается, когда Выбор рабочего режима (бит [1: 0]) равен 0x2 в регистре конфигурации передачи с выравниванием по битам SPI. А в 3-проводном режиме для входных и выходных данных используется одна и та же единственная линия данных. На следующем рисунке показан этот режим.

Рисунок 9-23. 3-проводной режим SPI.

9.3.3.7

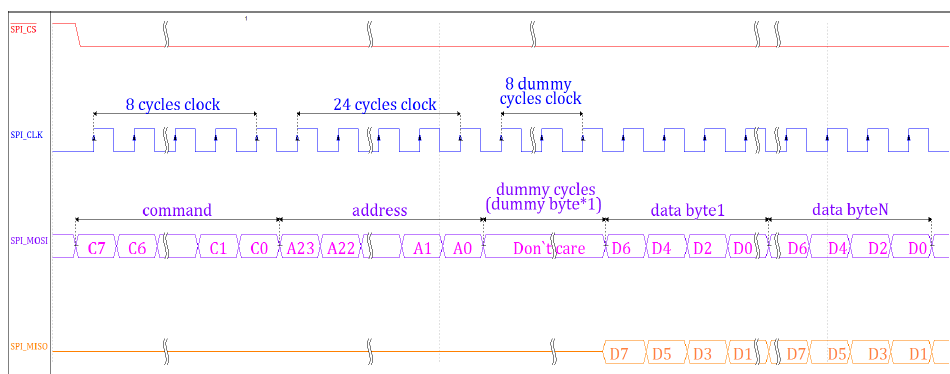

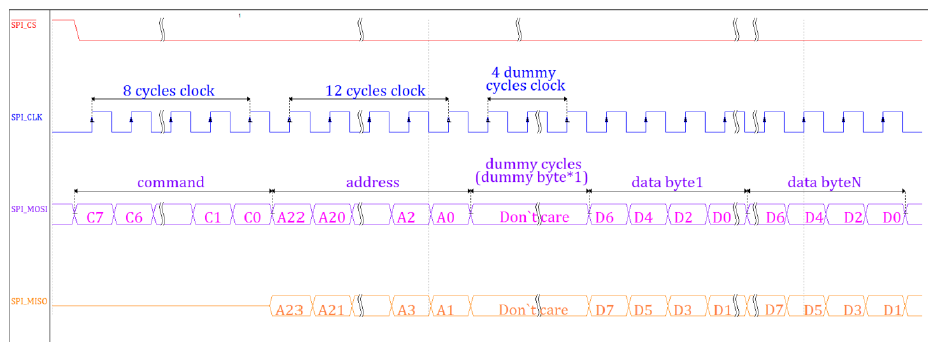

SPI Dual-Input / Dual-Output и Dual I / O Mode

Режим двойного чтения (SPI x2) выбирается, когда DRM (бит 28) установлен в регистре главного счетчика управления пакетами SPI. Использование двойного режима позволяет передавать данные на устройство или от него с удвоенной скоростью по сравнению со стандартными одномодовыми устройствами SPI, данные могут быть прочитаны на высокой скорости с использованием двух битов данных (MOSI и MISO) одновременно. На следующем рисунке показаны SPI с двумя входами и выходами

Рисунок 9-24. Режим двойного входа / двойного выхода SPI

В SPI с двойным входом / двойным выходом команда, адрес и фиктивные байты выводятся в единицах одного бита в последовательном режиме через строку SPI_MOSI, только байты данных выводятся (запись) и ввод (чтение) в единице. двойных битов через SPI_MOSI и SPI_MISO.

Рисунок 9-25. Режим двойного ввода / вывода SPI

В SPI с двойным вводом / выводом только байты команд выводятся в единицах одного бита в последовательном режиме через строку SPI_MOSI. Байты адреса и фиктивные байты выводятся в единицах двойных битов через SPI_MOSI и SPI_MISO. И байты данных выводятся (записываются) и вводятся (считываются) в единицах двойных битов через SPI_MOSI и SPI_MISO.

9.3.3.8

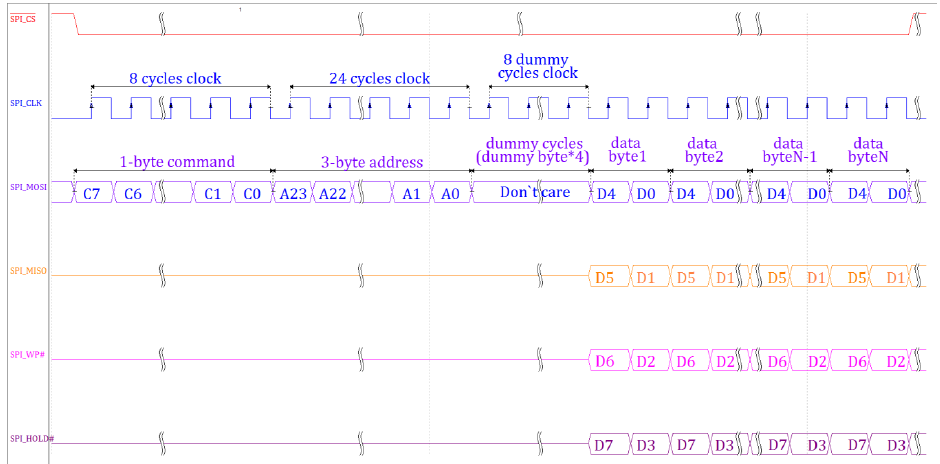

Режим SPI с четырьмя входами / четырьмя выходами

Режим четырехъядерного чтения (SPI x4) выбирается, когда Quad_EN (бит 29) установлен в регистре главного счетчика управления пакетами SPI. Использование четырехъядерного режима позволяет передавать данные на устройство или от него в 4 раза быстрее, чем стандартные одномодовые устройства SPI, данные могут быть прочитаны с высокой скоростью с использованием четырех битов данных (MOSI, MISO, IO2 (WP #) и IO3 ( УДЕРЖАТЬ #)) одновременно. На следующем рисунке показан SPI с четырьмя входами и четырьмя выходами.

Рисунок 9-26. Режим SPI с четырьмя входами и четырьмя выходами

В SPI с четырьмя входами / четырьмя выходами команда, адрес и фиктивные байты выводятся в единицах одного бита в последовательном режиме через строку SPI_MOSI. Только байты данных выводятся (записываются) и вводятся (считываются) в единицах четверных битов через SPI_MOSI, SPI_MISO, SPI_WP # и SPI_HOLD #.

9.3.3.9

Пакетная передача / прием в режиме ведущего

В ведущем режиме SPI пакет передачи и приема (байт в блоке) настраивается до того, как SPI передает последовательные данные между процессором и внешним устройством. Пакеты передачи записываются в MWTC (бит [23: 0]) главного регистра счетчика передачи SPI. Передаваемые пакеты в одиночном режиме перед автоматической отправкой фиктивного пакета записываются в STC (бит [23: 0]) регистра контрольного счетчика пакетов SPI. Для фиктивных данных контроллер SPI может автоматически отправлять перед получением путем записи DBC (бит [27:24]) в регистр главного счетчика управления пакетами SPI. Если пользователи не используют контроллер SPI для автоматической отправки фиктивных данных, то фиктивные пакеты используются в качестве счетчиков передачи для совместной записи в MWTC (бит [23: 0]) главного регистра счетчика передачи SPI. В ведущем режиме общее количество пакетов записывается в MBC (бит [23: 0]) регистра главного счетчика пакетов SPI. Когда все пакеты передачи и приема переданы, контроллер SPI отправит завершенное прерывание, в то же время контроллер SPI очистит DBC, MWTC и MBC.9.3.3.10

Пример режима SPI и конфигурация тактовой частоты

Контроллер SPI работает на частоте 3 кГц ~ 100 МГц на интерфейсе с внешними устройствами SPI. Внутренние часы SPI должны работать с той же частотой, что и исходящие часы в режиме ведущего. Для часов SPI выбираются разные источники синхронизации, SPI должен настраивать другой режим работы. Существует три режима работы: нормальный режим выборки, режим задержки полупериода выборки, режим задержки одного цикла выборки. Режим отсчета полупериода задержки является режимом по умолчанию контроллера SPI. Когда SPI работает на частоте 40 МГц или ниже 40 МГц, SPI может работать в обычном режиме выборки или в режиме задержки полупериода выборки. Когда SPI работает на частоте более 60 МГц, установка бита SDC в регистре управления передачей SPI на «1» делает внутреннюю точку выборки чтения с полупериодом. задержка SPI_CLK, которая используется в операции высокоскоростного чтения, чтобы уменьшить ошибку, вызванную временной задержкой передачи SPI_CLK между ведущим и ведомым.Различные конфигурации режима выборки SPI показаны в Таблице 9-11.

SPI Sample Mode SDM (bit13) SDC (bit11) Run Clock

9.3.3.11

Состояния ошибки SPI

Если возникнут какие-либо условия ошибки, оборудование установит соответствующие биты состояния в регистре состояния прерывания SPI и остановит передачу. Для контроллера SPI могут возникнуть следующие сценарии ошибок. (1) TX_FIFO Underrun Недополнение TX_FIFO происходит, когда CPU / DMA читает из TX FIFO, когда он пуст. В этом случае контроллер SPI завершит транзакцию и отметит бит ошибки вместе с битом TF_UDF в регистре состояния прерывания SPI. Контроллер SPI генерирует прерывание, если прерывания разрешены. Программное обеспечение должно очистить бит ошибки и бит TF_UDF. Чтобы начать новую транзакцию, программное обеспечение должно сбросить FIFO, записав в бит SRST (мягкий сброс) в регистре глобального контроллера SPI.(2) Переполнение TX_FIFO

Переполнение TX_FIFO происходит, когда CPU / DMA записывает в TX FIFO, когда он заполнен. В этом случае контроллер SPI завершит транзакцию и пометит бит ошибки вместе с битом TF_OVF в регистре состояния прерывания SPI. Контроллер SPI генерирует прерывание, если прерывания разрешены. Программное обеспечение должно очистить бит ошибки и бит TF_OVF. Чтобы начать новую транзакцию, программное обеспечение должно сбросить FIFO, записав в бит SRST (мягкий сброс) в регистре глобального контроллера SPI.(3) RX_FIFO Underrun

Недополнение RX_FIFO происходит, когда CPU / DMA читает из RX FIFO, когда он пуст. В этом случае контроллер SPI завершит транзакцию и пометит бит ошибки вместе с битом RF_UDF в регистре состояния прерывания SPI. Контроллер SPI генерирует прерывание, если прерывания разрешены. Программное обеспечение должно очистить бит ошибки и бит RF_UDF. Чтобы начать новую транзакцию, программное обеспечение должно сбросить FIFO, записав в бит SRST (мягкий сброс) в регистре глобального контроллера SPI.(4) Переполнение RX_FIFO

Переполнение RX_FIFO происходит, когда CPU / DMA записывает в RX FIFO, когда он заполнен. В этом случае контроллер SPI завершит транзакцию и отметит бит ошибки вместе с битом RF_OVF в регистре состояния прерывания SPI. Контроллер SPI генерирует прерывание, если прерывания разрешены. Программное обеспечение должно очистить бит ошибки и бит RF_OVF. Чтобы начать новую транзакцию, программное обеспечение должно сбросить FIFO, записав в бит SRST (мягкий сброс) в регистре глобального контроллера SPI.9.3.4. Рекомендации по программированию

9.3.4.1

CPU или DMA Operation

SPI передает последовательные данные между процессором и внешним устройством. CPU и DMA - два основных режима работы SPI. Для каждого SPI данные одновременно передаются (смещаются последовательно) и принимаются (смещаются последовательно). SPI имеет 2 канала, канал TX и канал RX. Канал TX имеет путь от TX FIFO к внешнему устройству. Канал RX имеет путь от внешнего устройства к RX FIFO. Запись данных: CPU или DMA должны записывать данные в регистр SPI_TXD, данные в регистре автоматически перемещаются в TX FIFO. Чтение данных: для чтения данных из RX FIFO, CPU или DMA должны получить доступ к регистру SPI_RXD, и данные автоматически отправляются в регистр SPI_RXD. В режиме CPU или DMA SPI отправляет завершенное прерывание (бит TC в регистре состояния прерывания SPI) процессору в конце каждой передачи.(1) .CPU режим

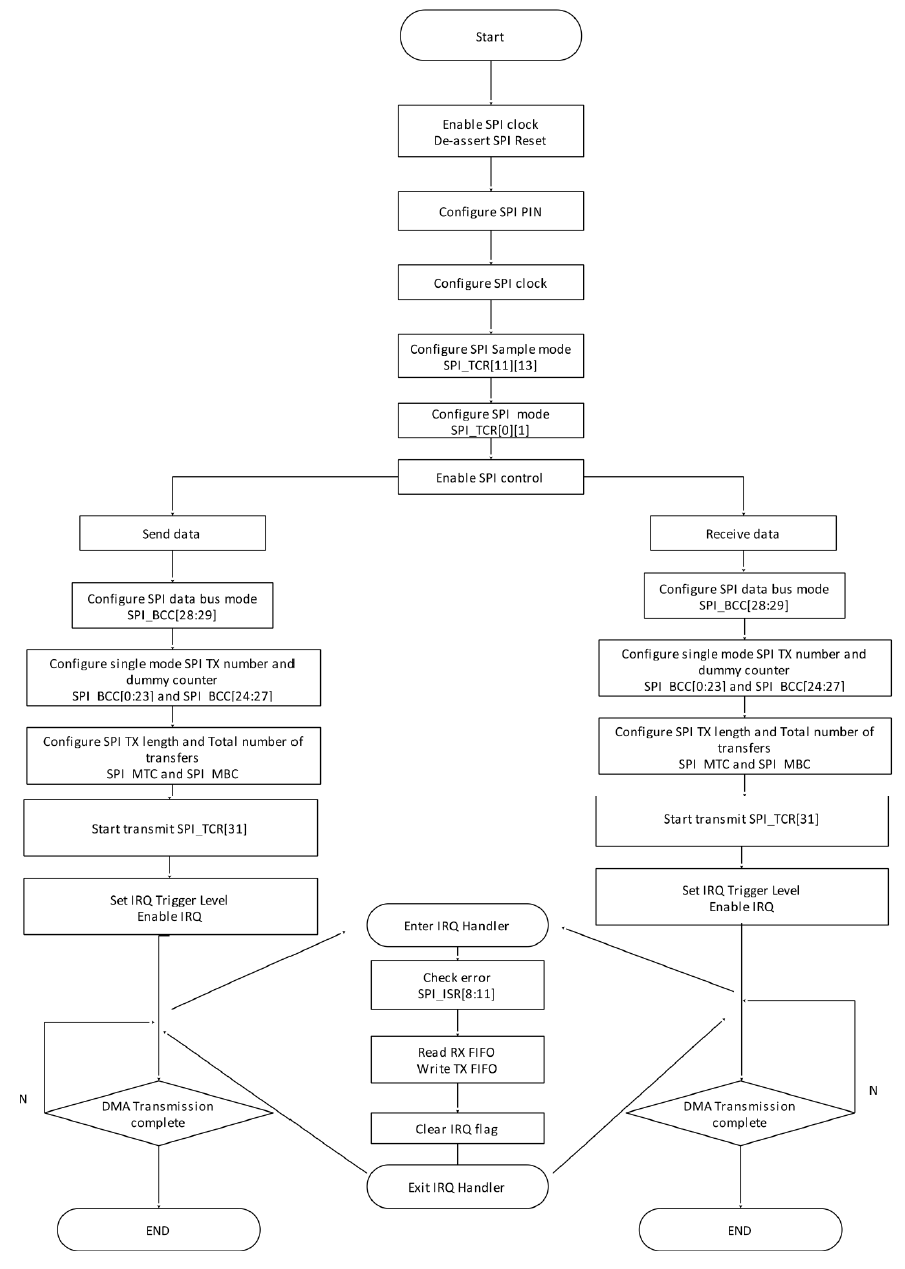

Рисунок 9-27. Запись / чтение данных SPI в режиме ЦП

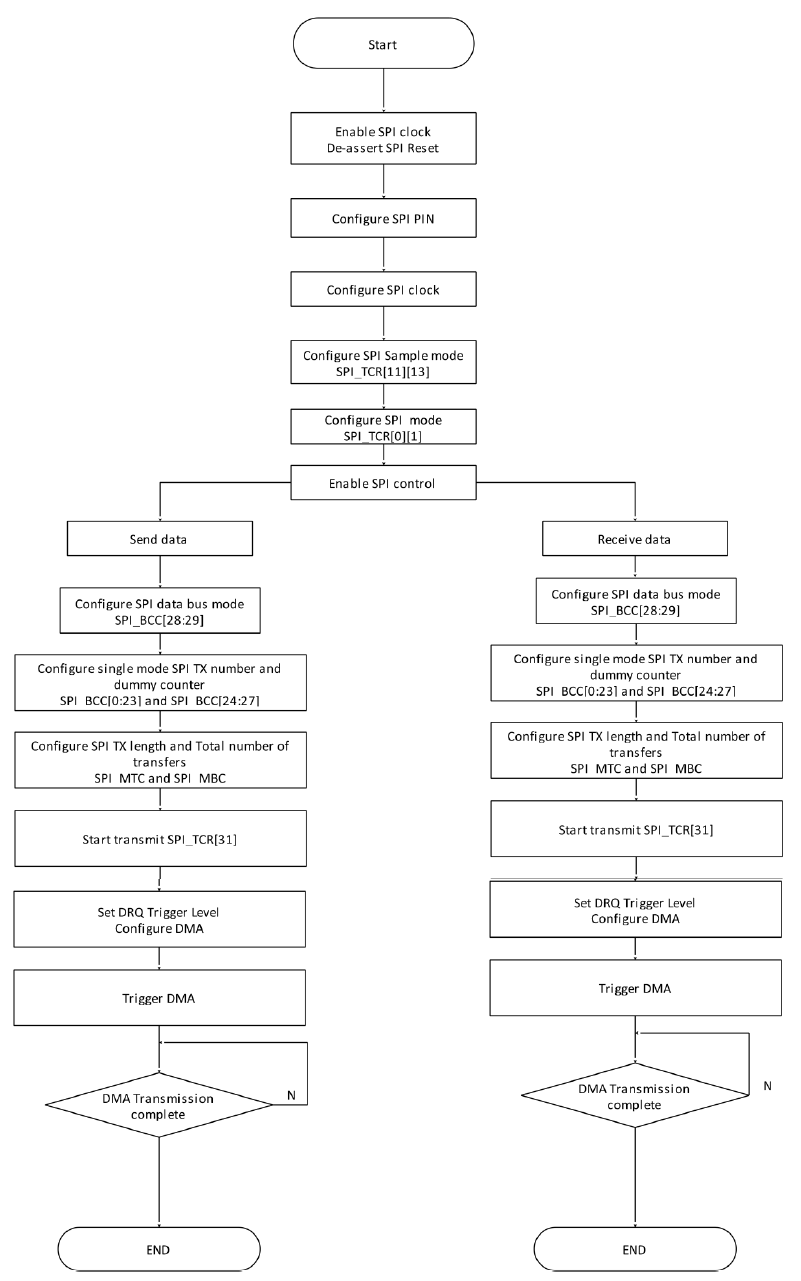

Рисунок 9-28. Запись / чтение данных SPI в режиме DMA

9.3.4.2

Калибровка цепочки задержки

SPI имеет одну цепочку задержки, которая используется для генерации задержки, чтобы обеспечить правильную синхронизацию между внутренним синхросигналом SPI и сигналами данных. Цепочка задержки состоит из 64 ячеек задержки. Время задержки одной ячейки задержки можно оценить с помощью калибровки цепи задержки.